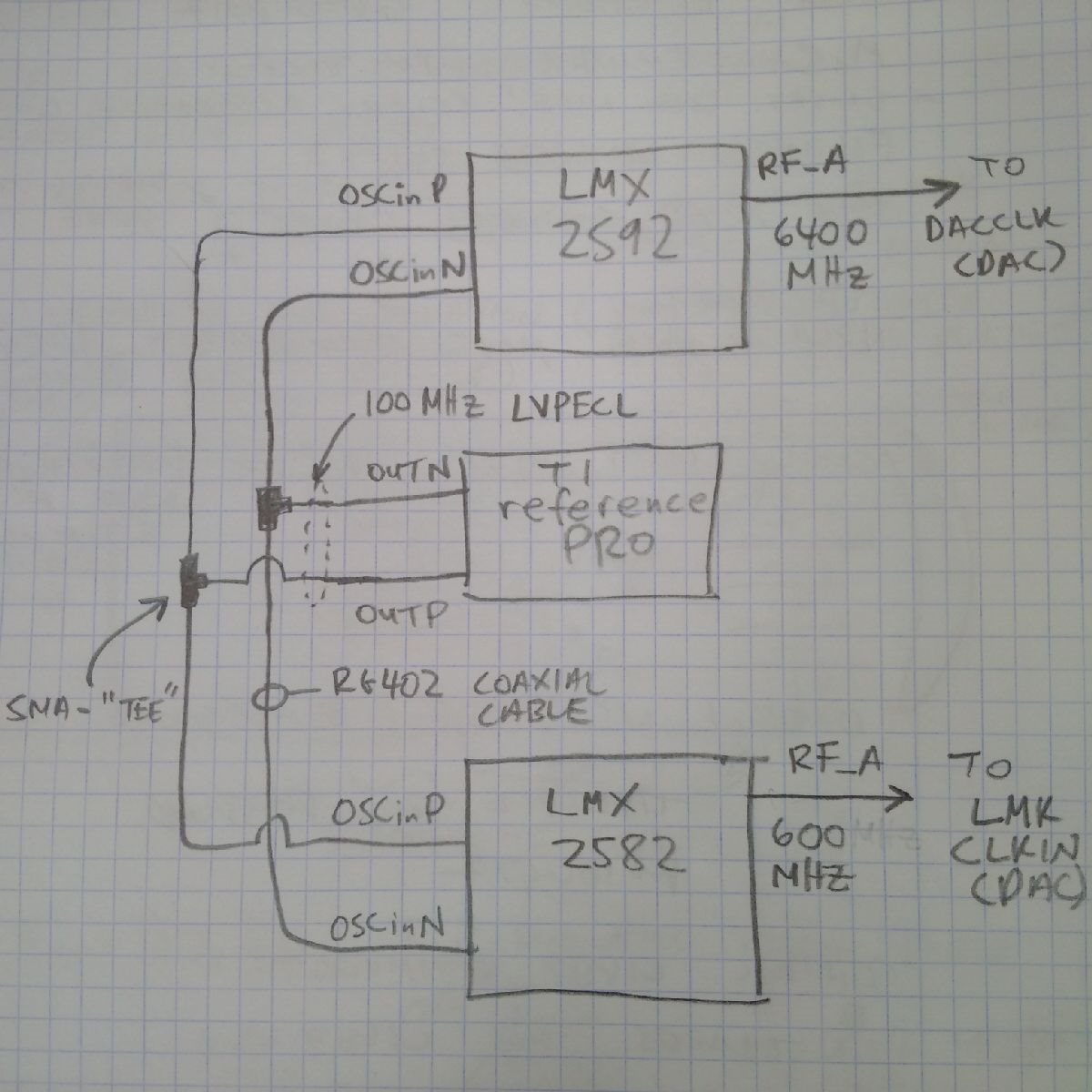

Other Parts Discussed in Thread: LMX2581, LMK04828BEVM, LMX2592, LMX2582

Hi Jim Seton,

I have been having some problems getting the DAC38RF82EVM to communicate with the TSW14J56EVM (no blinking LEDs, no successful transfer of external pattern file) when I use one particular HSDCPRO .ini file:

DAC38RF8x_LMF_823 <== Dual DACs (12 bit resolution), Real values, 4 Lanes, 2x Interpolation.

I am using an External DAC clock running at 6.4 GHz (~ 16 dBm tone w/o spurs, input into SMA "DACCLKP"). Using the exact same clock setup, I *am* able to use a related HSDCPRO .ini file:

DAC38RF8x_LMF_821 <== Dual DACs (14 bit resolution), Real values, 4 Lanes, 4x Interpolation.

With this .ini file, I am able to communicate with the TSW14J56 (blinking Tx CLK LED, no memory error), load a single tone, load an external pattern file, and measure the expected RF output on the Channel A and Channel B ports (SMAs J6/ IOUTA and J2/ IOUTB_SE.

Any idea why one configuration works fine and the other doesn't?

Ultimately I would like to run the DAC with the following set-up:

DAC38RF8x_LMF_823 <== Dual DACs (12 bit resolution), Real values, 4 Lanes, 1x Interpolation. Direct External Clock at 3.2 GHz

but I need to get an RF synthesizer (I'm thinking LMX2581) that will output a clean (no-spurs) tone @ 3.2 GHz.

Any advice you could give about working with the 12-bit Dual DAC configuration would be greatly appreciated.

Much Thanks,

Steve Krupa

PS: I'm running the latest GUI software versions for HDSCpro (v4.8) and for DAC38RF8x EVM GUI (v1.5)