Hello,

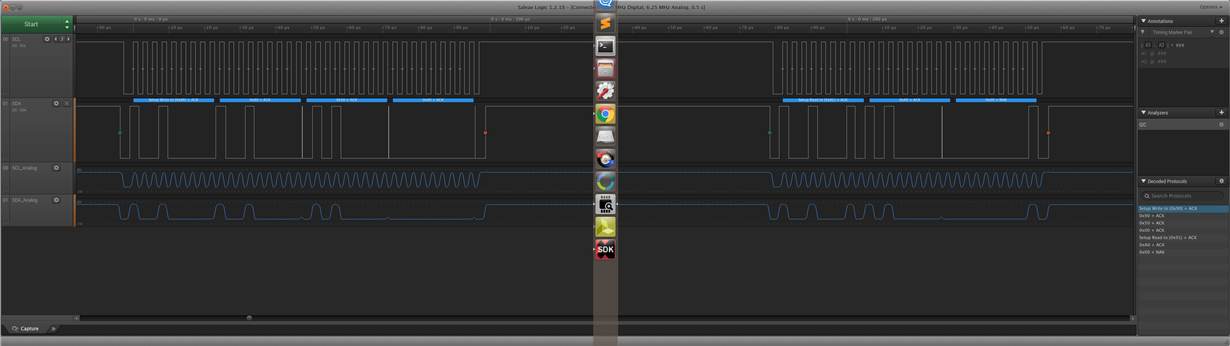

I have the DAC7678EVM and have it in the configuration described below. I've been able to successfully talk to the device at close to 400 kHz.

I'm trying to configure the device before outputting an analog voltage on any channel and I'm finding that the LDAC and Internal Reference registers are interfering with the Power-Down register.

----------------------------

Sequence:

- Write seq to Software Reset: 0x70, M 0x00, L 0x00

- Loop and read registers:

PWRDOWN_REG: 0x0000

CLEARCODE_REG: 0x0000

LDAC_REG: 0x0000

INTREF_STATIC_REG: 0x0000

INTREF_FLEX_REG: 0x0000

- Write seq to Clear Code Register: 0x50, M 0x00, L 0x30

- Read seq of Clear Code Register: M 0x00, L 0x03

- Write seq to LDAC Register: 0x60, M 0xFF, L 0x00

- Read seq of LDAC Register: M 0x00, L 0xFF

- Loop and read registers:

PWRDOWN_REG: 0x00F8 <--- WHY? Expected: M 0x0000

CLEARCODE_REG: 0x0003

LDAC_REG: 0x00FF

INTREF_STATIC_REG: 0x0000

INTREF_FLEX_REG: 0x0000

- Write seq to Power Down Register: 0x40, M 0x5F, L 0xE0

- Read seq of Clear Code Register: M 0x02, L 0xFF

- Loop and read registers:

PWRDOWN_REG: 0x02FF <--- GOOD

CLEARCODE_REG: 0x0003

LDAC_REG: 0x00FF

INTREF_STATIC_REG: 0x0000

INTREF_FLEX_REG: 0x0000

- Write seq to Internal Reference Static Register: 0x80, M 0x00, L 0x00

- Read seq of Internal Reference Static Register: M 0x00, L 0x00

- Write seq to Internal Reference Flexible Register: 0x90, M 0x50, L 0x00

- Read seq of Internal Reference Static Register: M 0xA0, L 0x00 <--- WHY? Expected: M 0x00, L 0x05

- Loop and read registers:

PWRDOWN_REG: 0x0280 <--- WHY? Why is this changing again?

CLEARCODE_REG: 0x0003

LDAC_REG: 0x00FF

INTREF_STATIC_REG: 0x0000

INTREF_FLEX_REG: 0xA000 <--- WHY? This doesn't make sense.

----------------------------

I'm having a hard time understanding why the Power Down register is changing value when I write to the LDAC or Internal Reference register. The I2C signals look good when using an logic analyzer/scope.

I'm using the following configuration...

JP1, JP2 and JP10 open

JP11 closed

JP4 closed 1/2 position

JP6 closed 1/2 position

JP7 closed 1/2 position

JP3 floating

JP8 and JP9 closed 2/3 position

+5V at J3.3

GND at J3.5 and J2.10

SCL at J2.16

SDA at J2.20

I appreciate any help in advance!

Phil