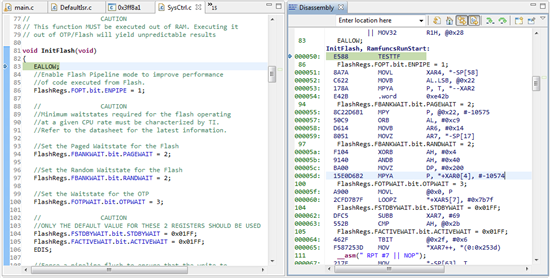

Hi everyone I have a problem with my Init flash function. I'm developping with a TMS320F28035 mounted into a custom board and at the very first instruction of the InitFlash() function the program go to the illegal isr trap.

Here you can see the begining of my main.c :

#include "DSP28x_Project.h" // DSP28x Headerfile

#include "DSP2803x_Cla_defines.h"

#include "DSP2803x_Gpio.h"

#include "Interrupt.h"

#include "i2c.h"

// Include the test header file whose name is based on the test name

// which is defined by the macro TEST on the command line

#include "shared.h"

#define CLARAM0_ENABLE 1

#define CLARAM1_ENABLE 1

//CLA ISRs

__interrupt void cla1_task1_isr( void );

__interrupt void cla1_task2_isr( void );

__interrupt void cla1_task3_isr( void );

__interrupt void cla1_task4_isr( void );

__interrupt void cla1_task5_isr( void );

__interrupt void cla1_task6_isr( void );

__interrupt void cla1_task7_isr( void );

__interrupt void cla1_task8_isr( void );

__interrupt void cpu_timer1_isr(void);

//Linker defined vars

extern Uint16 Cla1Prog_Start;

extern Uint16 Cla1funcsLoadStart;

extern Uint16 Cla1funcsLoadEnd;

extern Uint16 Cla1funcsRunStart;

extern Uint16 Cla1funcsLoadSize;

extern Uint16 Cla1mathTablesLoadStart;

extern Uint16 Cla1mathTablesRunStart;

extern Uint16 Cla1mathTablesLoadSize;

extern Uint16 RamfuncsLoadStart;

extern Uint16 RamfuncsLoadSize;

extern Uint16 RamfuncsRunStart;

Uint16 loop, loop2;

float32 f32VOCID_Card_Nb;

tstepsParameters stepsParameters[NB_SENSORS];

tParametric Parametric[NB_SENSORS];

tHeaterManagment HeaterManagment[NB_SENSORS];

// Main Function

void main(void)

{

// Step 1: Setup the system clock

/* Disable the watchdog timer, initialize the system clock,

* PLL and configure the peripheral clock.

*/

InitSysCtrl();

InitGpio();

// Step 2: Initialize PIE control

/* Intialize PIE control, disable all interrupts and

* then copy over the PIE Vector table from BootROM to RAM

*/

DINT;

InitPieCtrl();

IER = 0x00000000;

IFR = 0x00000000;

InitPieVectTable();

/* Assign user defined ISR to the PIE vector table */

EALLOW;

PieVectTable.CLA1_INT1 = &cla1_task1_isr;

PieVectTable.CLA1_INT2 = &cla1_task2_isr;

PieVectTable.CLA1_INT3 = &cla1_task3_isr;

PieVectTable.CLA1_INT4 = &cla1_task4_isr;

PieVectTable.CLA1_INT5 = &cla1_task5_isr;

PieVectTable.CLA1_INT6 = &cla1_task6_isr;

PieVectTable.CLA1_INT7 = &cla1_task7_isr;

PieVectTable.CLA1_INT8 = &cla1_task8_isr;

PieVectTable.TINT1 = &cpu_timer1_isr;

PieVectTable.ADCINT1 = &adc_isr;

PieVectTable.I2CINT1A = &i2c_int1a_isr;

PieVectTable.XINT1 = &xint1_isr;

EDIS;

InitCpuTimers();

ConfigCpuTimer(&CpuTimer1, 60, 5000000);

// To ensure precise timing, use write-only instructions to write to the entire register. Therefore, if any

// of the configuration bits are changed in ConfigCpuTimer and InitCpuTimers (in DSP2803x_CpuTimers.h), the

// below settings must also be updated.

CpuTimer1Regs.TCR.all = 0x4000; // Use write-only instruction to set TSS bit = 0

//Copy over the CLA code and Tables

memcpy(&Cla1funcsRunStart, &Cla1funcsLoadStart, (Uint32)&Cla1funcsLoadSize);

memcpy(&Cla1mathTablesRunStart, &Cla1mathTablesLoadStart, (Uint32)&Cla1mathTablesLoadSize);

memcpy(&RamfuncsLoadStart, &RamfuncsRunStart, (Uint32)&RamfuncsLoadSize);

InitFlash();

InitAdc(); // Initialise l'ADC du DSP

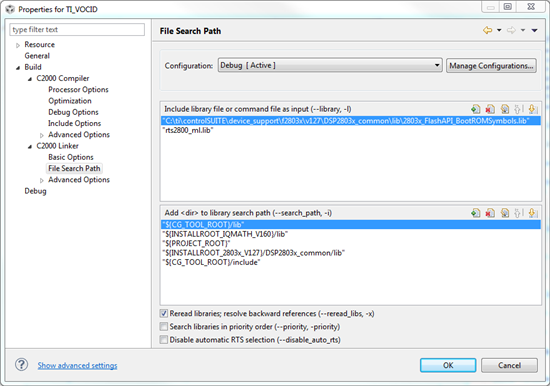

And my .cmd file

/*

//###########################################################################

//

// FILE: F28035_CLA_C.cmd

//

// TITLE: Linker Command File For F28035 Device

//

//###########################################################################

// $TI Release: F2803x C/C++ Header Files and Peripheral Examples V127 $

// $Release Date: March 30, 2013 $

//###########################################################################

*/

/* ======================================================

// For Code Composer Studio V2.2 and later

// ---------------------------------------

// In addition to this memory linker command file,

// add the header linker command file directly to the project.

// The header linker command file is required to link the

// peripheral structures to the proper locations within

// the memory map.

//

// The header linker files are found in <base>\DSP2803x_Headers\cmd

//

// For BIOS applications add: DSP2803x_Headers_BIOS.cmd

// For nonBIOS applications add: DSP2803x_Headers_nonBIOS.cmd

========================================================= */

/* ======================================================

// For Code Composer Studio prior to V2.2

// --------------------------------------

// 1) Use one of the following -l statements to include the

// header linker command file in the project. The header linker

// file is required to link the peripheral structures to the proper

// locations within the memory map */

/* Uncomment this line to include file only for non-BIOS applications */

/* -l DSP2803x_Headers_nonBIOS.cmd */

/* Uncomment this line to include file only for BIOS applications */

/* -l DSP2803x_Headers_BIOS.cmd */

/* 2) In your project add the path to <base>\DSP2803x_headers\cmd to the

library search path under project->build options, linker tab,

library search path (-i).

/*========================================================= */

/* Define the memory block start/length for the F28035

PAGE 0 will be used to organize program sections

PAGE 1 will be used to organize data sections

Notes:

Memory blocks on F2803x are uniform (ie same

physical memory) in both PAGE 0 and PAGE 1.

That is the same memory region should not be

defined for both PAGE 0 and PAGE 1.

Doing so will result in corruption of program

and/or data.

L0 memory block is mirrored - that is

it can be accessed in high memory or low memory.

For simplicity only one instance is used in this

linker file.

Contiguous SARAM memory blocks or flash sectors can be

be combined if required to create a larger memory block.

*/

_Cla1Prog_Start = _Cla1funcsRunStart;

-heap 0x200

-stack 0x200

// Define a size for the CLA scratchpad area that will be used

// by the CLA compiler for local symbols and temps

// Also force references to the special symbols that mark the

// scratchpad are.

// CLA_SCRATCHPAD_SIZE = 0x100;

--undef_sym=__cla_scratchpad_end

--undef_sym=__cla_scratchpad_start

MEMORY

{

PAGE 0: /* Program Memory */

/* Memory (RAM/FLASH/OTP) blocks can be moved to PAGE1 for data allocation */

RAMM0 : origin = 0x000050, length = 0x0003B0 /* on-chip RAM block M0 */

RAML3 : origin = 0x009000, length = 0x001000 /* on-chip RAM block L3 */

OTP : origin = 0x3D7800, length = 0x000400 /* on-chip OTP */

FLASHH : origin = 0x3E8000, length = 0x002000 /* on-chip FLASH */

FLASHG : origin = 0x3EA000, length = 0x002000 /* on-chip FLASH */

FLASHF : origin = 0x3EC000, length = 0x002000 /* on-chip FLASH */

FLASHE : origin = 0x3EE000, length = 0x002000 /* on-chip FLASH */

FLASHD : origin = 0x3F0000, length = 0x002000 /* on-chip FLASH */

FLASHC : origin = 0x3F2000, length = 0x002000 /* on-chip FLASH */

FLASHA : origin = 0x3F6000, length = 0x001F80 /* on-chip FLASH */

CSM_RSVD : origin = 0x3F7F80, length = 0x000076 /* Part of FLASHA. Program with all 0x0000 when CSM is in use. */

BEGIN : origin = 0x3F7FF6, length = 0x000002 /* Part of FLASHA. Used for "boot to Flash" bootloader mode. */

CSM_PWL_P0 : origin = 0x3F7FF8, length = 0x000008 /* Part of FLASHA. CSM password locations in FLASHA */

IQTABLES : origin = 0x3FE000, length = 0x000B50 /* IQ Math Tables in Boot ROM */

IQTABLES2 : origin = 0x3FEB50, length = 0x00008C /* IQ Math Tables in Boot ROM */

IQTABLES3 : origin = 0x3FEBDC, length = 0x0000AA /* IQ Math Tables in Boot ROM */

ROM : origin = 0x3FF27C, length = 0x000D44 /* Boot ROM */

RESET : origin = 0x3FFFC0, length = 0x000002 /* part of boot ROM */

VECTORS : origin = 0x3FFFC2, length = 0x00003E /* part of boot ROM */

PAGE 1 : /* Data Memory */

/* Memory (RAM/FLASH/OTP) blocks can be moved to PAGE0 for program allocation */

/* Registers remain on PAGE1 */

BOOT_RSVD : origin = 0x000000, length = 0x000050 /* Part of M0, BOOT rom will use this for stack */

RAMM1 : origin = 0x000400, length = 0x000400 /* on-chip RAM block M1 */

RAML0 : origin = 0x008000, length = 0x000800 /* on-chip RAM block L0 */

// CLARAM0 : origin = 0x008800, length = 0x000400

// CLARAM1 : origin = 0x008C00, length = 0x000400

CLARAM : origin = 0x008800, length = 0x000800

CLA1_MSGRAMLOW : origin = 0x001480, length = 0x000080

CLA1_MSGRAMHIGH : origin = 0x001500, length = 0x000080

FLASHB : origin = 0x3F4000, length = 0x002000 /* on-chip FLASH */

}

/* Allocate sections to memory blocks.

Note:

codestart user defined section in DSP28_CodeStartBranch.asm used to redirect code

execution when booting to flash

ramfuncs user defined section to store functions that will be copied from Flash into RAM

*/

SECTIONS

{

/* Allocate program areas: */

.cinit : > FLASHA PAGE = 0

.pinit : > FLASHA, PAGE = 0

// .text : > FLASHC PAGE = 0

.text: { *(.text) } >> FLASHE|FLASHF|FLASHG PAGE = 0

codestart : > BEGIN PAGE = 0

ramfuncs : LOAD = FLASHD,

RUN = RAMM0,

LOAD_START(_RamfuncsLoadStart),

LOAD_SIZE(_RamfuncsLoadSize),

RUN_START(_RamfuncsRunStart),

PAGE = 0

csmpasswds : > CSM_PWL_P0 PAGE = 0

csm_rsvd : > CSM_RSVD PAGE = 0

/* Allocate uninitalized data sections: */

.stack : > RAMM1 PAGE = 1

.cio : > RAML0 PAGE = 1

.sysmem : > RAMM1 PAGE = 1

.ebss : > RAML0 PAGE = 1

.esysmem : > RAML0 PAGE = 1

/* Initalized sections go in Flash */

/* For SDFlash to program these, they must be allocated to page 0 */

.econst : > FLASHA PAGE = 0

.switch : > FLASHA PAGE = 0

/* Allocate IQ math areas: */

IQmath : > FLASHA PAGE = 0 /* Math Code */

IQmathTables : > IQTABLES, PAGE = 0, TYPE = NOLOAD

// .bss_cla : > CLARAM1, PAGE = 1

.bss_cla : > CLARAM, PAGE = 1

Cla1Prog : LOAD = FLASHD,

RUN = RAML3,

LOAD_START(_Cla1funcsLoadStart),

LOAD_END(_Cla1funcsLoadEnd),

RUN_START(_Cla1funcsRunStart),

LOAD_SIZE(_Cla1funcsLoadSize),

PAGE = 0

Cla1ToCpuMsgRAM : > CLA1_MSGRAMLOW, PAGE = 1

CpuToCla1MsgRAM : > CLA1_MSGRAMHIGH, PAGE = 1

// Cla1DataRam0 : > CLARAM0, PAGE = 1

// Cla1DataRam1 : > CLARAM1, PAGE = 1

Cla1DataRam : > CLARAM, PAGE = 1

GROUP : LOAD = FLASHB,

RUN = CLARAM, //RUN = CLARAM1,

LOAD_START(_Cla1mathTablesLoadStart),

LOAD_END(_Cla1mathTablesLoadEnd),

RUN_START(_Cla1mathTablesRunStart),

LOAD_SIZE(_Cla1mathTablesLoadSize),

PAGE = 1

{

CLA1mathTables

.const_cla

}

CLAscratch :

{ *.obj(CLAscratch)

. += CLA_SCRATCHPAD_SIZE;

*.obj(CLAscratch_end) } > CLARAM,

// *.obj(CLAscratch_end) } > CLARAM1,

PAGE = 1

/* Uncomment the section below if calling the IQNexp() or IQexp()

functions from the IQMath.lib library in order to utilize the

relevant IQ Math table in Boot ROM (This saves space and Boot ROM

is 1 wait-state). If this section is not uncommented, IQmathTables2

will be loaded into other memory (SARAM, Flash, etc.) and will take

up space, but 0 wait-state is possible.

*/

/*

IQmathTables2 : > IQTABLES2, PAGE = 0, TYPE = NOLOAD

{

IQmath.lib<IQNexpTable.obj> (IQmathTablesRam)

}

*/

/* Uncomment the section below if calling the IQNasin() or IQasin()

functions from the IQMath.lib library in order to utilize the

relevant IQ Math table in Boot ROM (This saves space and Boot ROM

is 1 wait-state). If this section is not uncommented, IQmathTables2

will be loaded into other memory (SARAM, Flash, etc.) and will take

up space, but 0 wait-state is possible.

*/

/*

IQmathTables3 : > IQTABLES3, PAGE = 0, TYPE = NOLOAD

{

IQmath.lib<IQNasinTable.obj> (IQmathTablesRam)

}

*/

/* .reset is a standard section used by the compiler. It contains the */

/* the address of the start of _c_int00 for C Code. /*

/* When using the boot ROM this section and the CPU vector */

/* table is not needed. Thus the default type is set here to */

/* DSECT */

.reset : > RESET, PAGE = 0, TYPE = DSECT

vectors : > VECTORS PAGE = 0, TYPE = DSECT

}

/*

//===========================================================================

// End of file.

//===========================================================================

*/

I really don't understand what's happening ...

Best regards

Nicolas Sizorn