Other Parts Discussed in Thread: LM3478,

Hello

I recently have been in contact with you regarding simulation problems when using LM3478 in SEPIC topology. However, I wanted to use the LM5155 for my design and you gave me the transient model for it to simulate the circuit.

https://e2e.ti.com/support/power-management/f/196/p/855129/3184699?tisearch=e2e-sitesearch&keymatch=lm3478%20simulation#3184699

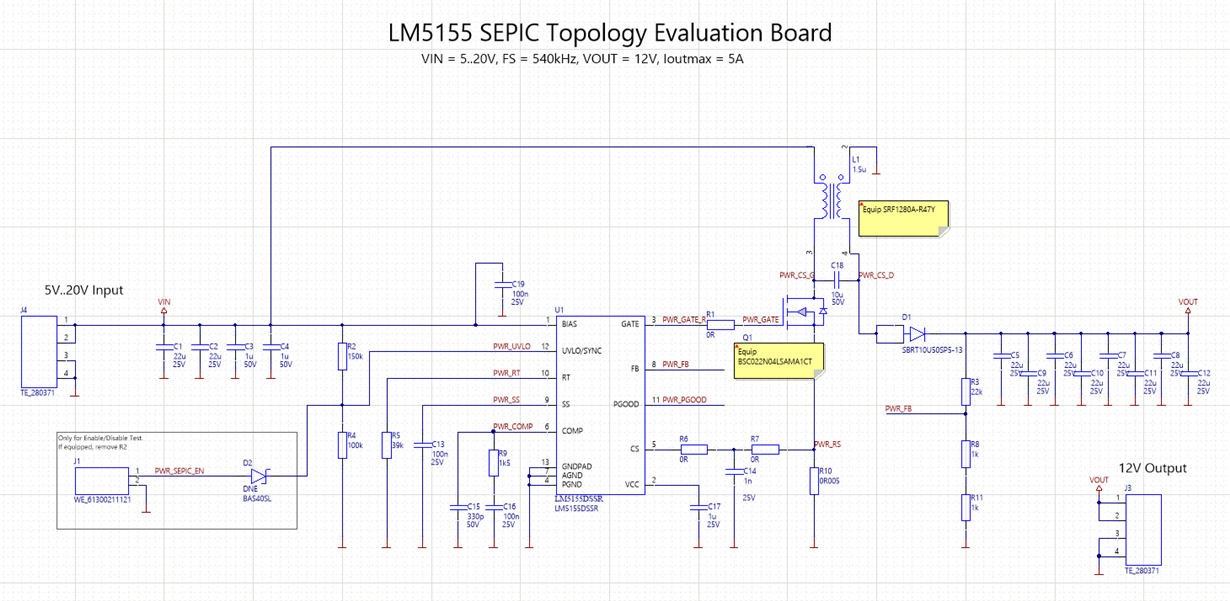

In the meantime I made an evaluation board to test the SEPIC circuitry with LM5155. I did the calculations/dimensioning according to AN-1484.

Requirements are:

Vin = 5..20V, Vout=12V, Ioutmax=5A

Calculations gave me:

L1=L2=700nH (coupled) (used SRF1280A-R47Y)

You can see the other components used in the schematics below. I encountered several problems which I’d like to share and also hope for some tips to improve the circuitry. Can you see any major dimensioning errors?

Problems:

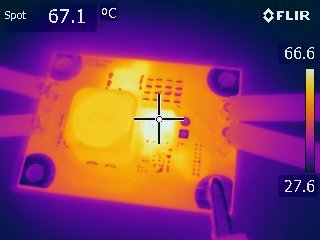

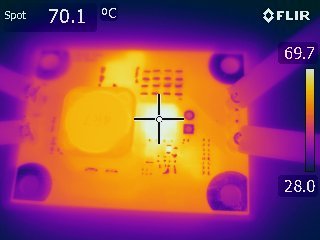

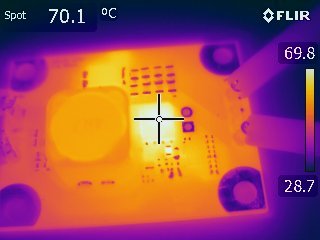

When drawing Iout=1A (far from the maximum), the Mosfet (type BSC022N04LSATMA1) already heats up to 85°C in appr. 2min. The power dissipation in the Mosfet is far too high. According to my calculations with Iout=1A, the Mosfet power dissipation should be 226mW. However, 226mW should not lead to such heating of the component, hence I assume the switching losses to be higher than expected. I’m aware, that the Mosfet on my board is not mounted on a 6cm^2 copper square as cooling area (as stated in the Mosfet datasheet to have RthJAmax=50K/W).

Of course lowering the switching frequency could be an option, however I’m interested in understanding the differences between the calculations vs. evaluation board.

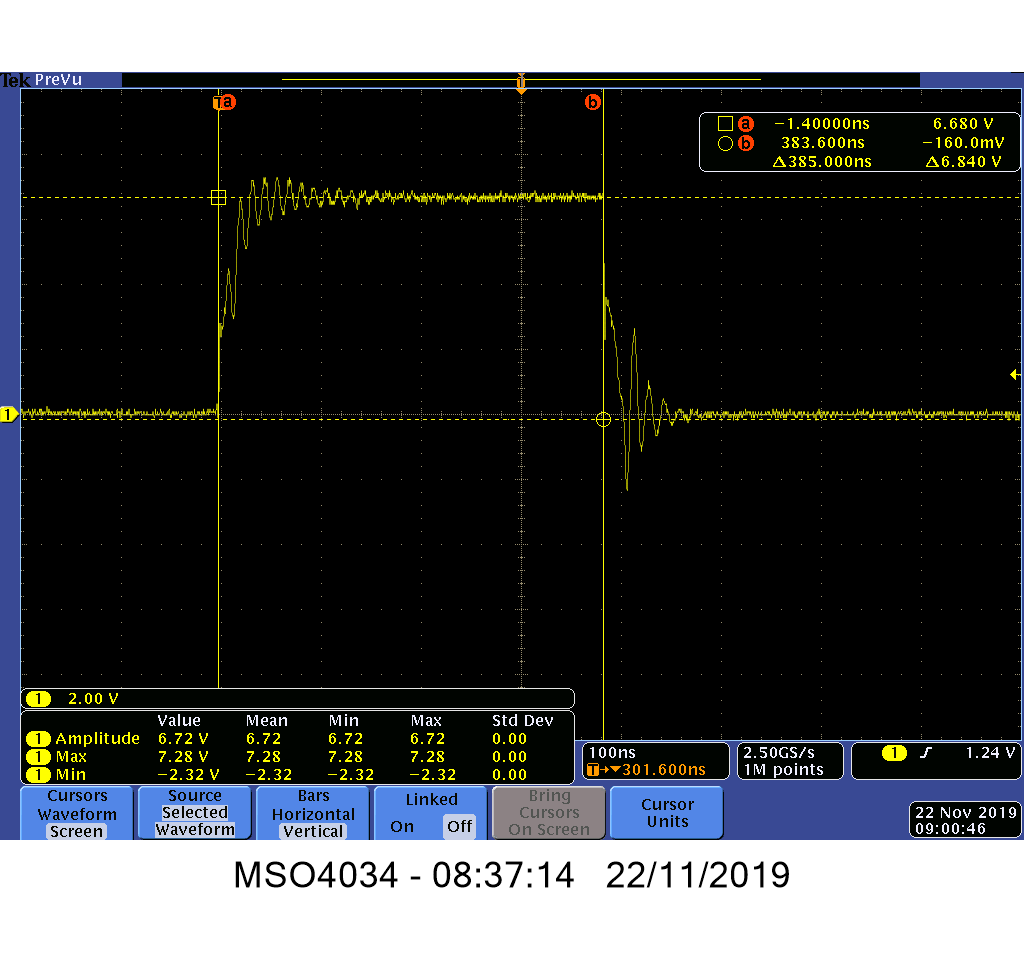

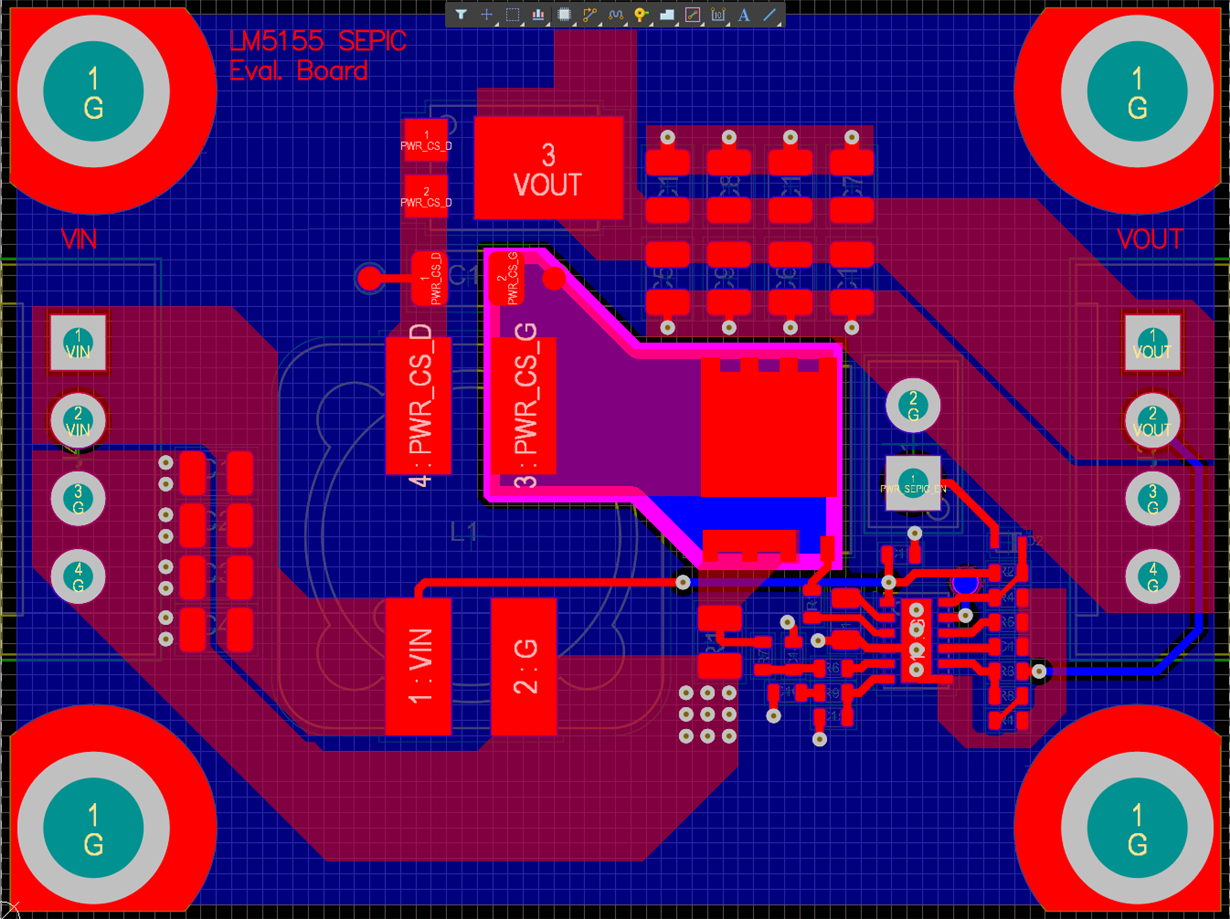

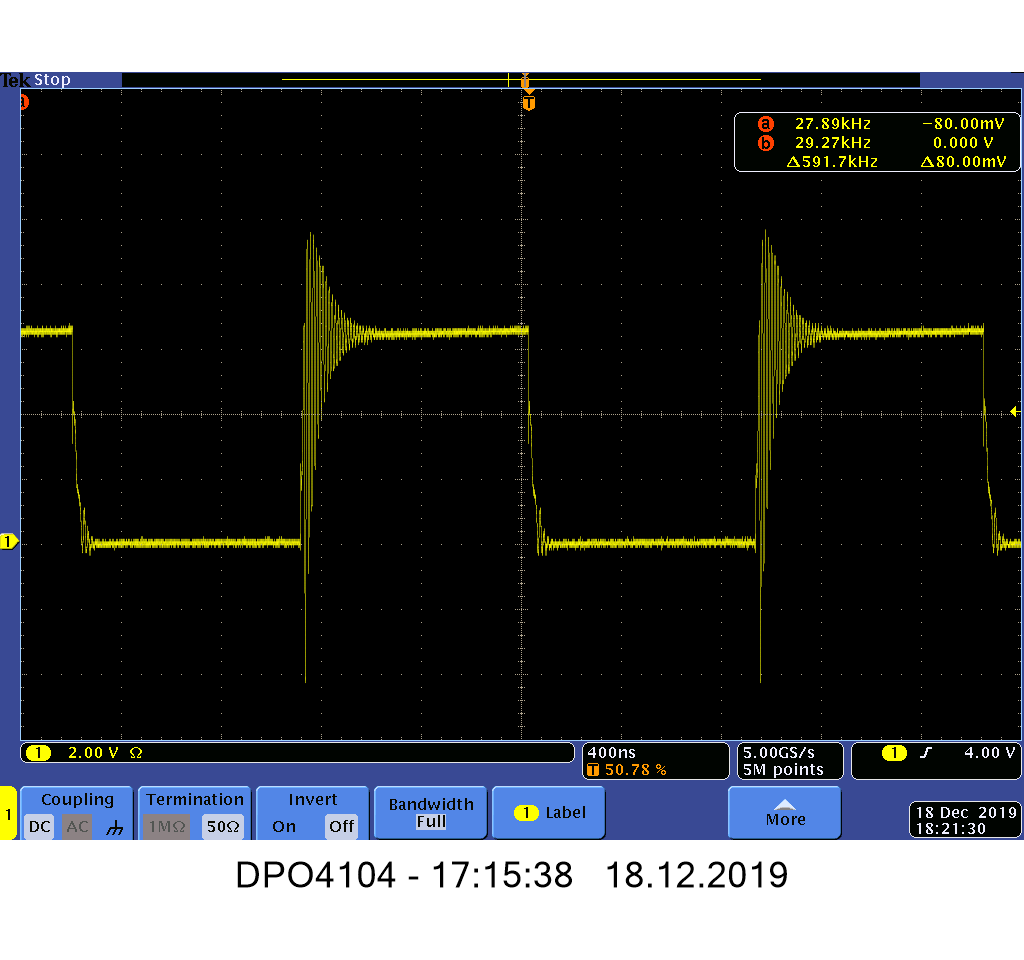

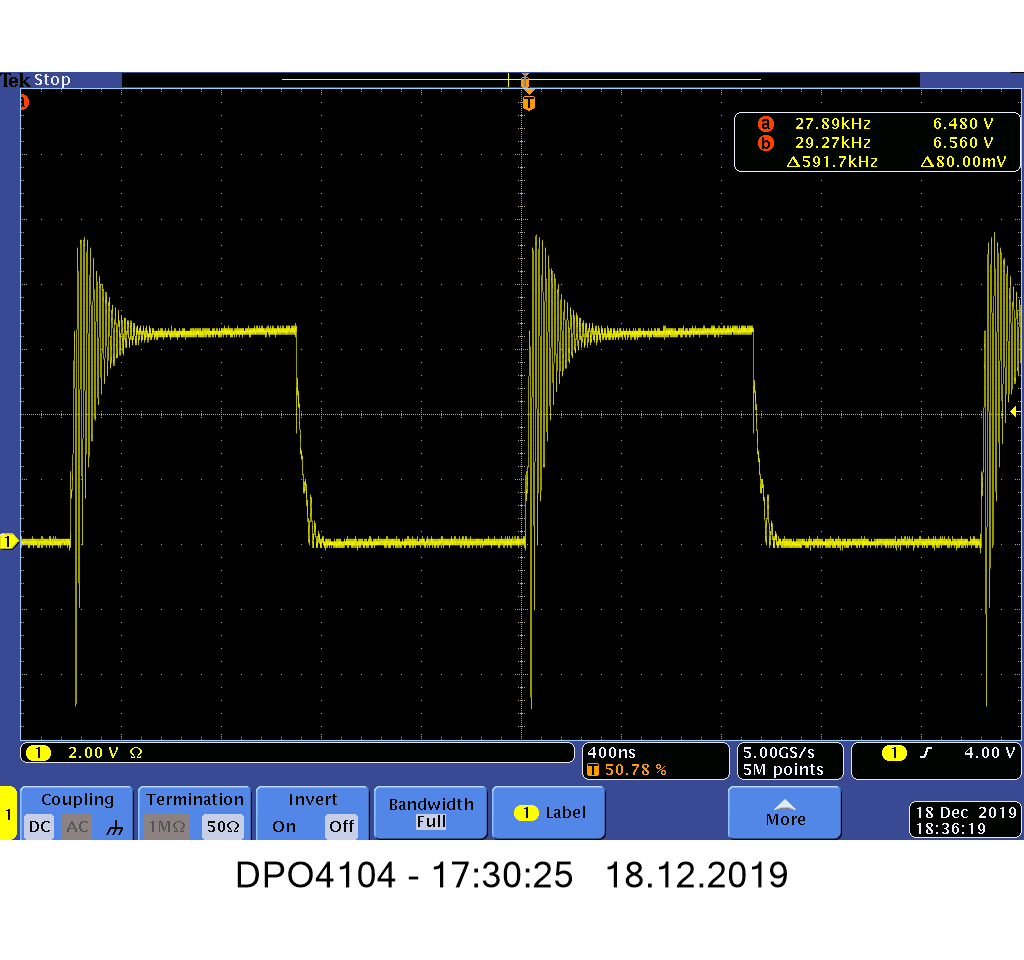

Measuring the gate voltage of the Mosfet, I observe more or less steep edges, but gate ringing exists. Gate ringing usually exists due to parasitics along the gate loop. However, the gate loop in my layout is quite small, the connection from the converter to the gate also. Do you have an idea where this gate ringing comes from? I also added my layout below.

Inserting a gate resistor to damp the ringing did not help, since it also slows down the rise of the gate voltage (and the longer switching time led to even more power dissipation in the Mosfet).

Do you have an idea where this gate ringing comes from and how to deal with it?

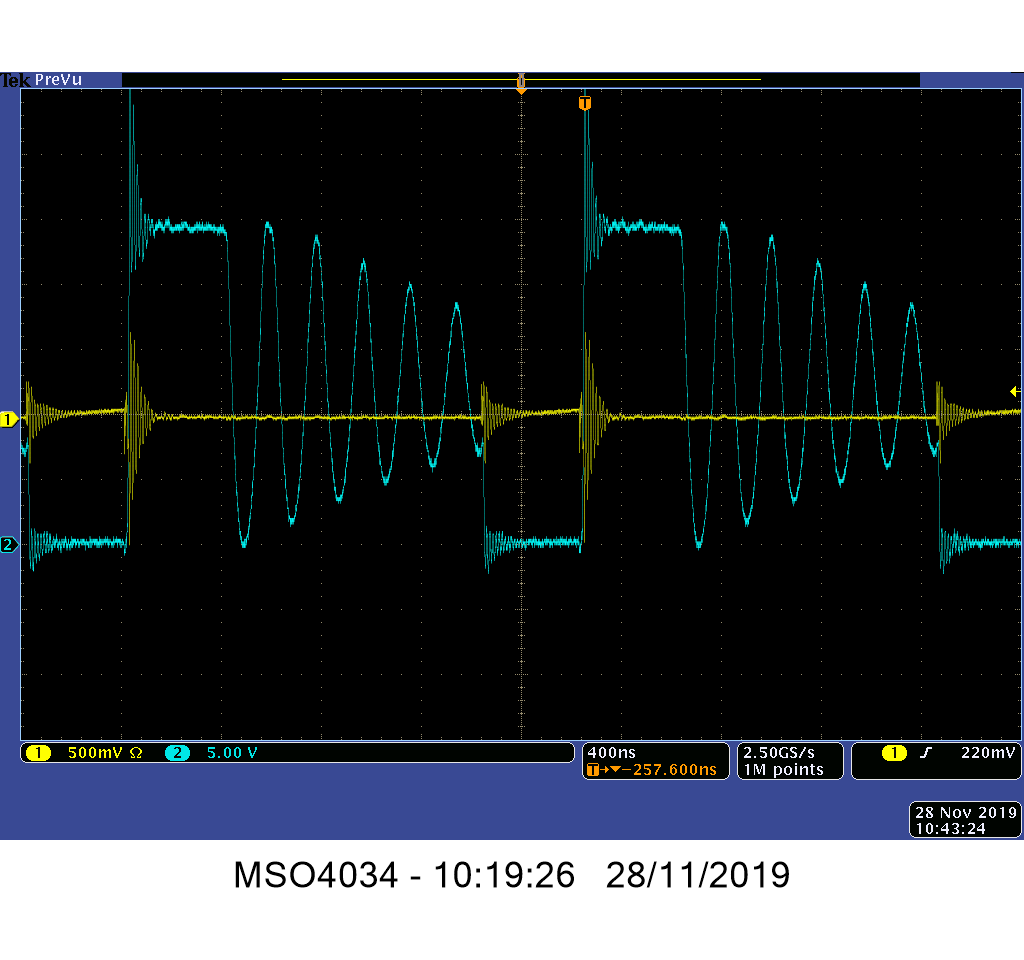

I also measured the drain voltage of the Mosfet (CH2) and the voltage across the sense resistor (R10). I assume the oscillations/noise to come from the grate ringing.

Simulation of the circuit did not show such behaviour and worked quite well. Please find the circuit also below.

Thanks in advance for any help!

Best regards,

Martin