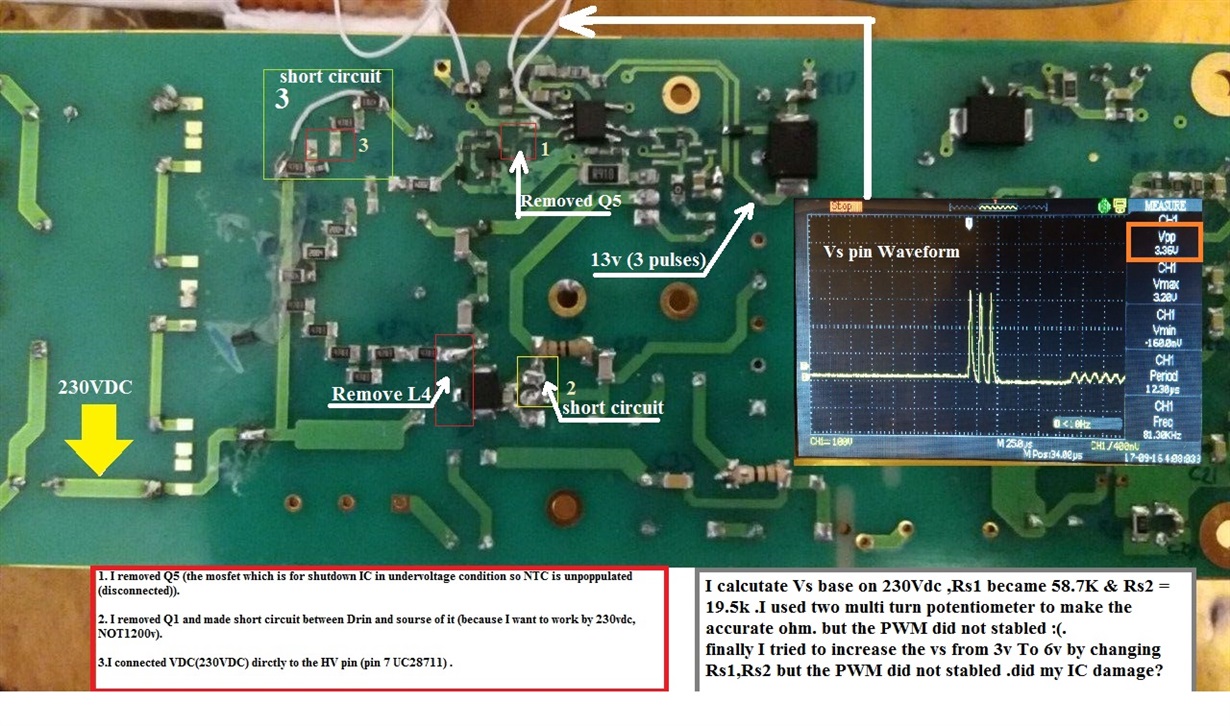

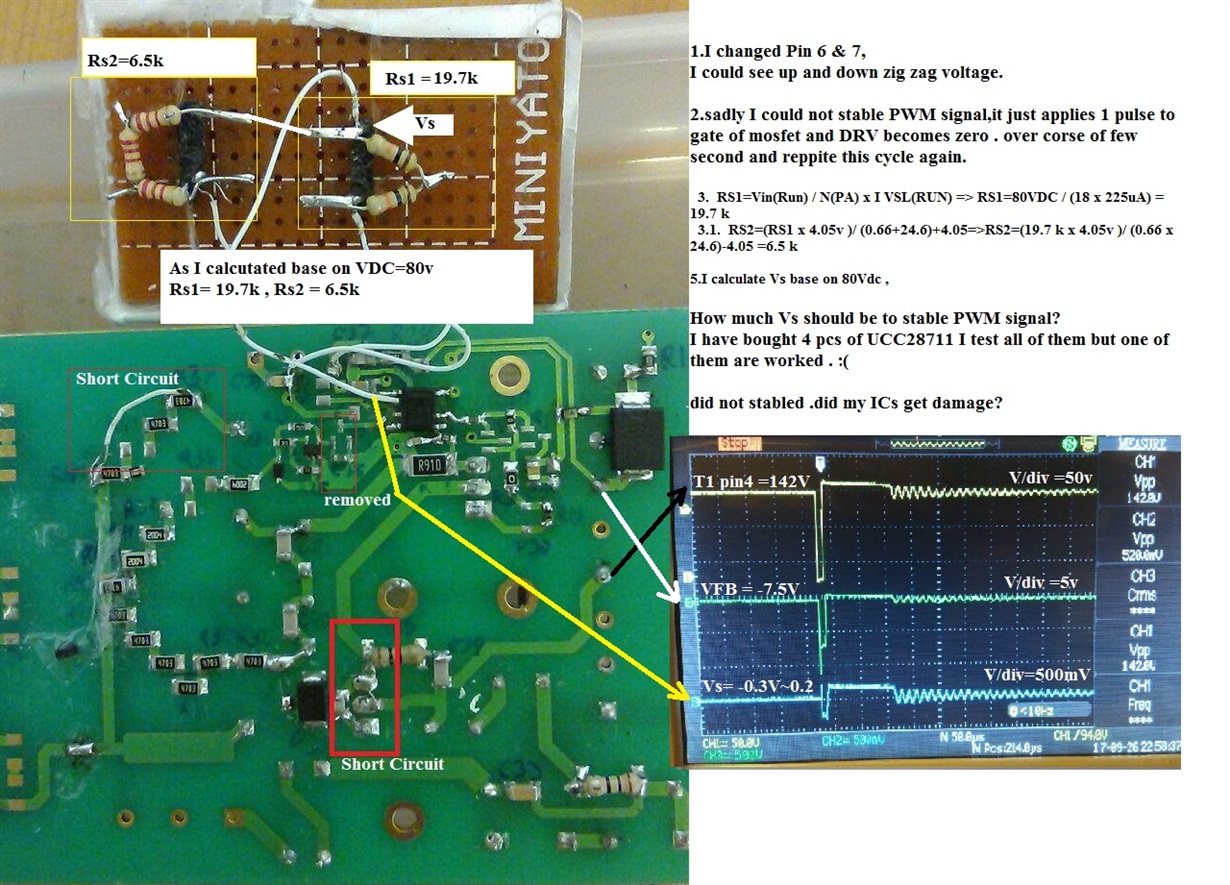

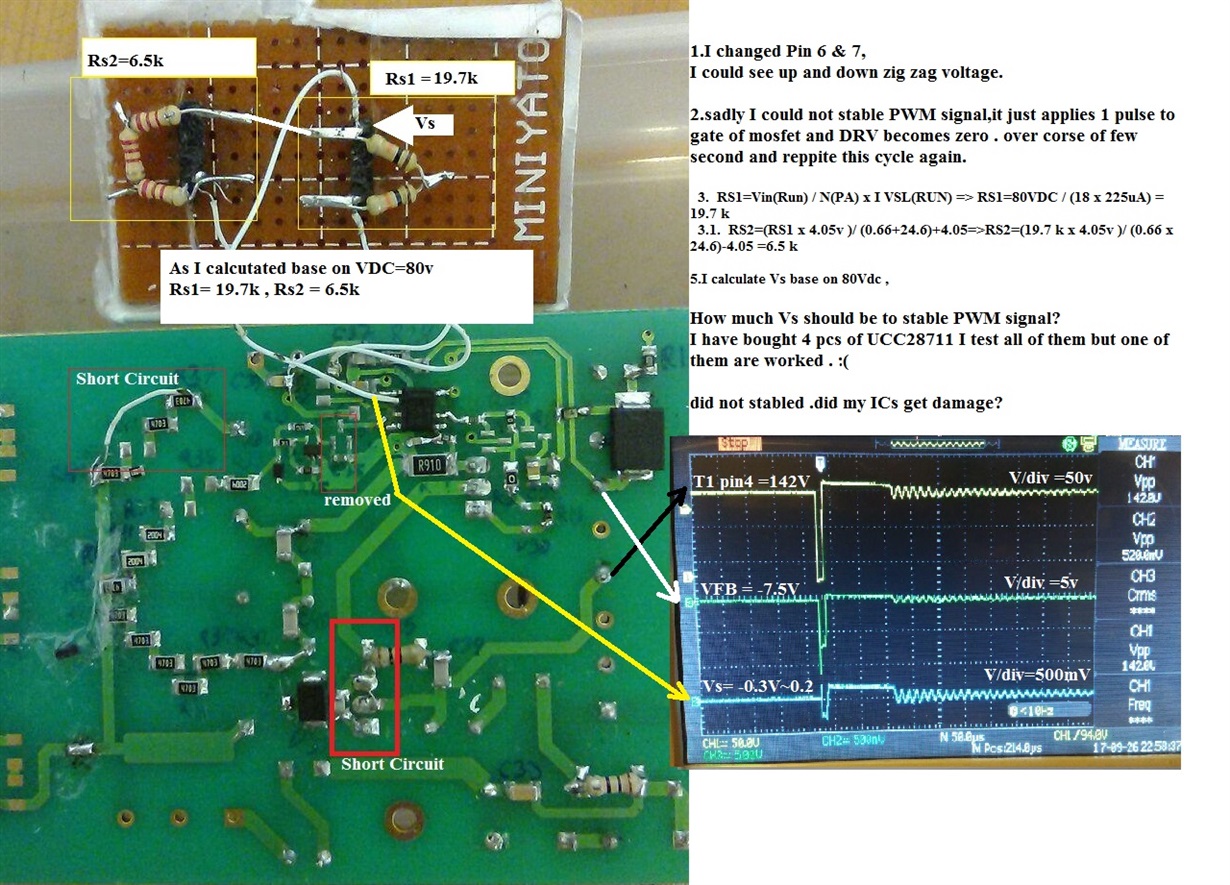

I assambeled TIDA-00173 board but the CDD is not charged I try to disconnect D29 , Q25 and connected separate power supply with 24V to see gate drive pulse for (initiate three small gate drive pulses) but it didnt happen :( . i think NTC pin when is disconect it should have 5 v But sadly It does not have any voltage on it .

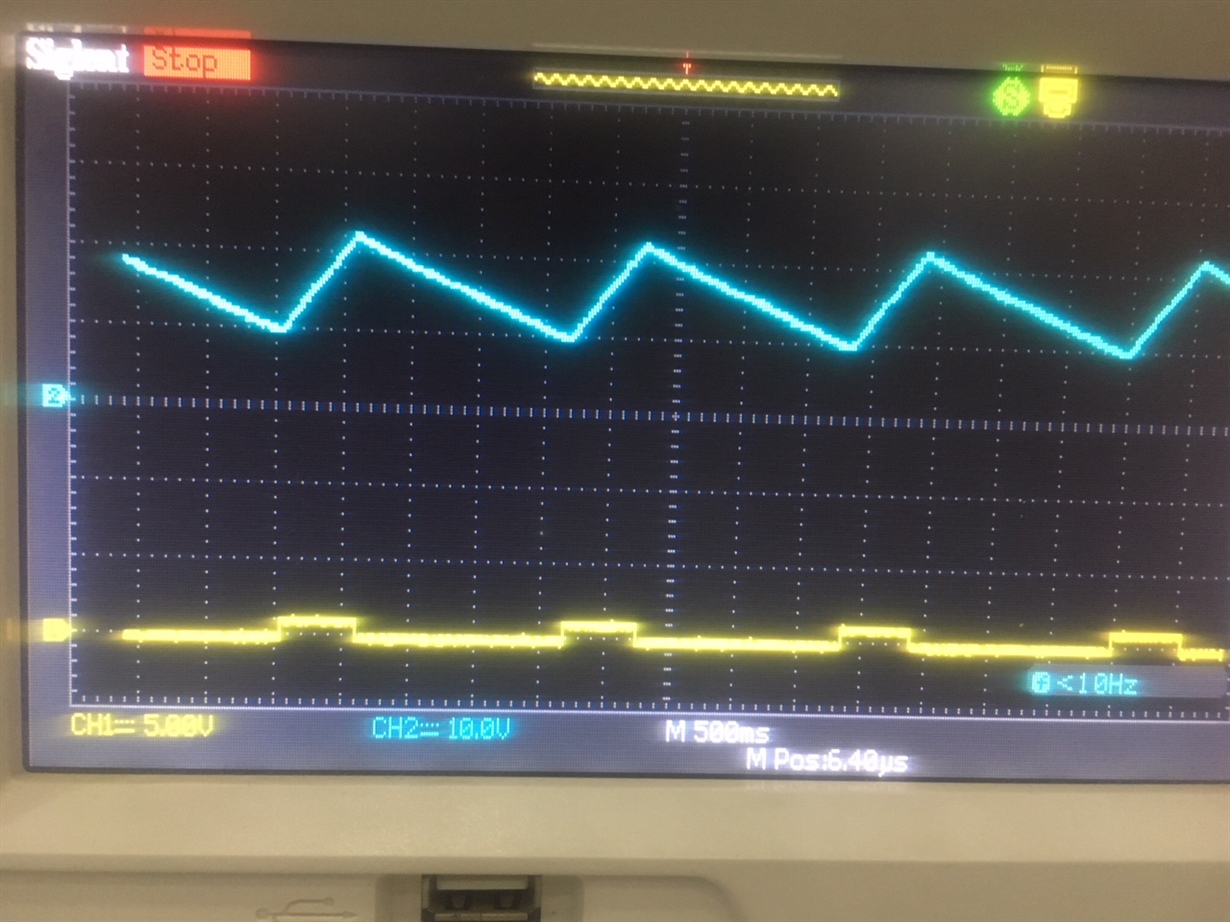

so how should I know if UC28711 is fine ? is it enough to conect VDD= 24 volt, NTC disconected, GND =0 volt(GND) , HV disconected,CS disconected,DRV for test conected to scop to seeinitiate three small gate drive pulses?

Please Help me to solve it thanks :)

thanks for attention