Other Parts Discussed in Thread: TIDA-00778

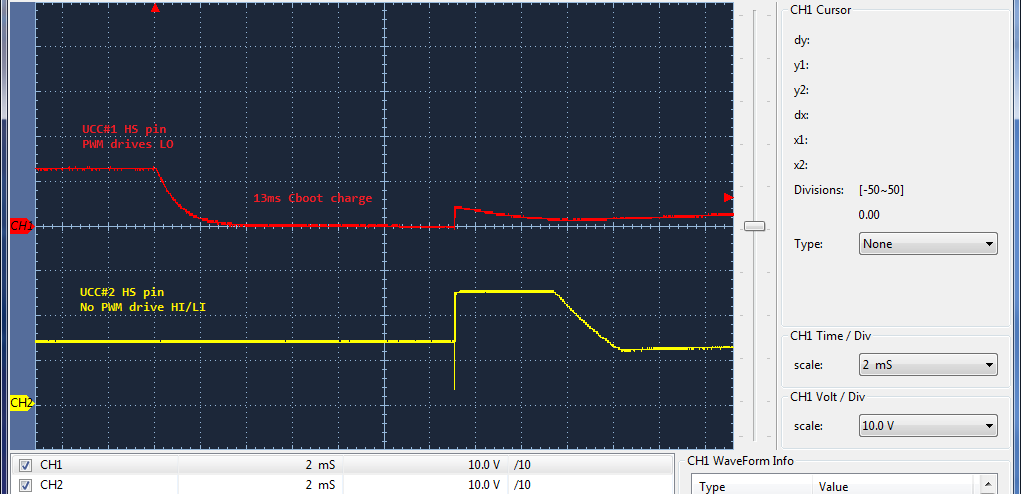

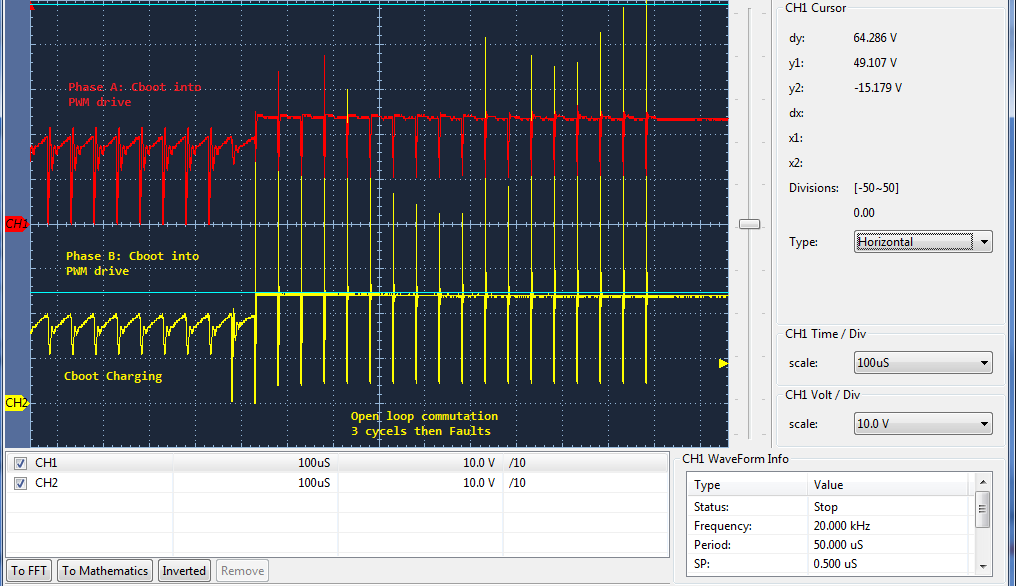

Finally seeing a pattern where one UCC Cboot charge cycle causes another static but enabled UCC HO output to suddenly go active without HI input triggering it.

The CH1 - HS of 1st UCC as LO pin receives 13ms PWM @50us periods to charge Cboot. CH2 - HS of 2nd UCC sits quietly but EN is logic high 3.0v and the 3rd UCC is effecting in the same way.

The HS pins of all UCC feed the MCU ADC channels as with other vendors gate drivers same basic circuit. We never see this issue in past but fight for weeks to stop this insane behavior even taking unusual steps in software to control Cboot charging cycles can not rectify this hardware failure. The only UCC not being much effected it the first Cboot charge or maybe even with delay added get the second to charge but the 3rd then jumps HO up like crazy. Surely TI tested UCC in three phase commutation high impedance ADC channels monitoring HS does not effect HO drive?

How is the 2nd/3rd UCC HO pin being trigged active state when no signal is input to HI or LO and VDD is highly filtered?