Hello Sir,

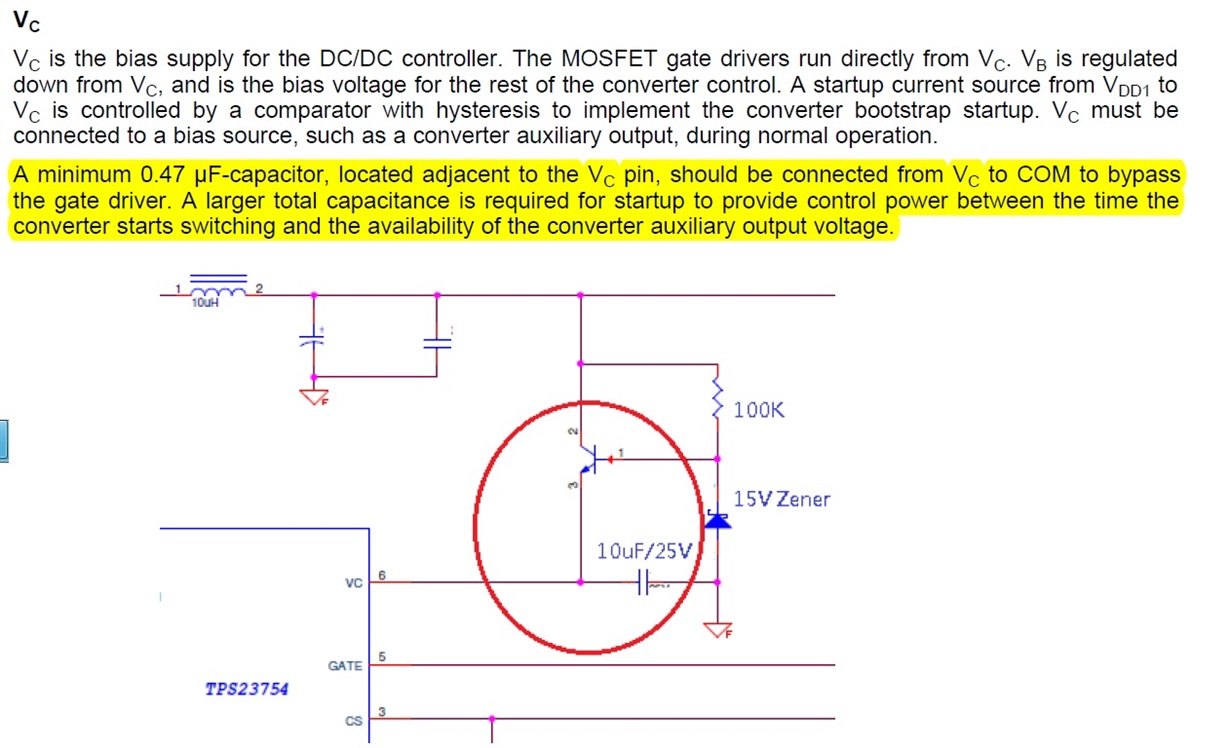

We have implemented a non-isolation POE design by using TPS23754. To generate a bias voltage for Vc (pin 6),

we used a "transistor series voltage regulator" (please see the following diagram) to generate 14.3V source voltage.

Since there is a requirement to add a minimum 0.47uF capacitor to Vc pin, we set this capacitor to 10uF. It end up a high

temperature on the transistor of series regulator. We try to reduce the capacitor value to 1uF and then we got 9-deg C down.

My questions are :

1. how to decide the value of capacitor add to Vc pin? (data sheet mention that minimum 0.47uF between Vc and ARTN and

a larger capacitor to power start up)

2. " a larger capacitor to power startup" How large should it be enough? Is there any formula to calculate it?

3. Can it work If I select a 1uF capacitor for the Vc pin ? Any side effect occur when the capacitor is changed from 10uF to 1uF?

Thanks~