Hi,

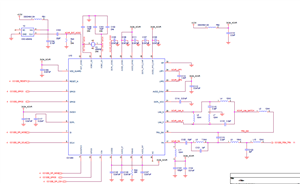

I want to use synchronous serial mode for CC1200. But the received bit stream seems completely wrong. So I want to make sure the register setting is correct. The register setting comes from smartRF studio. Can TI hellp to check whether it is no problem?

Best Regards

Yang

<html><head>

<style>

body {background-color:#dde;}

caption {font-weight:bold; font-size:16px;margin-left:30px}

th { text-align:left; background-color:#f00; color:#fff}

table { background-color: #eec; font-size:9px;margin:10px}

</style>

</head>

<body><table border=1 cellpadding=5 cellspacing=0>

<caption>CC1200 registers</caption>

<tr><th>Name</th><th>Address</th><th>Value</th>

<th>Description</th></tr><tr><td>IOCFG2<td>0x0001</td><td>0x08</td><td>GPIO2 IO Pin Configuration</td></tr>

<tr><td>IOCFG0<td>0x0003</td><td>0x09</td><td>GPIO0 IO Pin Configuration</td></tr>

<tr><td>SYNC_CFG1<td>0x0008</td><td>0xA8</td><td>Sync Word Detection Configuration Reg. 1</td></tr>

<tr><td>SYNC_CFG0<td>0x0009</td><td>0x23</td><td>Sync Word Detection Configuration Reg. 0</td></tr>

<tr><td>DEVIATION_M<td>0x000A</td><td>0x47</td><td>Frequency Deviation Configuration</td></tr>

<tr><td>MODCFG_DEV_E<td>0x000B</td><td>0x0C</td><td>Modulation Format and Frequency Deviation Configur..</td></tr>

<tr><td>DCFILT_CFG<td>0x000C</td><td>0x4B</td><td>Digital DC Removal Configuration</td></tr>

<tr><td>PREAMBLE_CFG1<td>0x000D</td><td>0x00</td><td>Preamble Length Configuration Reg. 1</td></tr>

<tr><td>PREAMBLE_CFG0<td>0x000E</td><td>0x8A</td><td>Preamble Detection Configuration Reg. 0</td></tr>

<tr><td>IQIC<td>0x000F</td><td>0xD8</td><td>Digital Image Channel Compensation Configuration</td></tr>

<tr><td>CHAN_BW<td>0x0010</td><td>0x08</td><td>Channel Filter Configuration</td></tr>

<tr><td>MDMCFG1<td>0x0011</td><td>0x06</td><td>General Modem Parameter Configuration Reg. 1</td></tr>

<tr><td>MDMCFG0<td>0x0012</td><td>0x05</td><td>General Modem Parameter Configuration Reg. 0</td></tr>

<tr><td>SYMBOL_RATE2<td>0x0013</td><td>0xA4</td><td>Symbol Rate Configuration Exponent and Mantissa [1..</td></tr>

<tr><td>SYMBOL_RATE1<td>0x0014</td><td>0x7A</td><td>Symbol Rate Configuration Mantissa [15:8]</td></tr>

<tr><td>SYMBOL_RATE0<td>0x0015</td><td>0xE1</td><td>Symbol Rate Configuration Mantissa [7:0]</td></tr>

<tr><td>AGC_REF<td>0x0016</td><td>0x2A</td><td>AGC Reference Level Configuration</td></tr>

<tr><td>AGC_CS_THR<td>0x0017</td><td>0x01</td><td>Carrier Sense Threshold Configuration</td></tr>

<tr><td>AGC_CFG1<td>0x001B</td><td>0x12</td><td>Automatic Gain Control Configuration Reg. 1</td></tr>

<tr><td>AGC_CFG0<td>0x001C</td><td>0x80</td><td>Automatic Gain Control Configuration Reg. 0</td></tr>

<tr><td>FIFO_CFG<td>0x001D</td><td>0x00</td><td>FIFO Configuration</td></tr>

<tr><td>FS_CFG<td>0x0020</td><td>0x12</td><td>Frequency Synthesizer Configuration</td></tr>

<tr><td>PKT_CFG2<td>0x0026</td><td>0x01</td><td>Packet Configuration Reg. 2</td></tr>

<tr><td>PKT_CFG1<td>0x0027</td><td>0x00</td><td>Packet Configuration Reg. 1</td></tr>

<tr><td>PKT_CFG0<td>0x0028</td><td>0x20</td><td>Packet Configuration Reg. 0</td></tr>

<tr><td>PKT_LEN<td>0x002E</td><td>0xFF</td><td>Packet Length Configuration</td></tr>

<tr><td>IF_MIX_CFG<td>0x2F00</td><td>0x1C</td><td>IF Mix Configuration</td></tr>

<tr><td>TOC_CFG<td>0x2F02</td><td>0x03</td><td>Timing Offset Correction Configuration</td></tr>

<tr><td>MDMCFG2<td>0x2F05</td><td>0x02</td><td>General Modem Parameter Configuration Reg. 2</td></tr>

<tr><td>FREQ2<td>0x2F0C</td><td>0x5C</td><td>Frequency Configuration [23:16]</td></tr>

<tr><td>FREQ1<td>0x2F0D</td><td>0x0F</td><td>Frequency Configuration [15:8]</td></tr>

<tr><td>FREQ0<td>0x2F0E</td><td>0x5C</td><td>Frequency Configuration [7:0]</td></tr>

<tr><td>IF_ADC1<td>0x2F10</td><td>0xEE</td><td>Analog to Digital Converter Configuration Reg. 1</td></tr>

<tr><td>IF_ADC0<td>0x2F11</td><td>0x10</td><td>Analog to Digital Converter Configuration Reg. 0</td></tr>

<tr><td>FS_DIG1<td>0x2F12</td><td>0x04</td><td>Frequency Synthesizer Digital Reg. 1</td></tr>

<tr><td>FS_DIG0<td>0x2F13</td><td>0x55</td><td>Frequency Synthesizer Digital Reg. 0</td></tr>

<tr><td>FS_CAL1<td>0x2F16</td><td>0x40</td><td>Frequency Synthesizer Calibration Reg. 1</td></tr>

<tr><td>FS_CAL0<td>0x2F17</td><td>0x0E</td><td>Frequency Synthesizer Calibration Reg. 0</td></tr>

<tr><td>FS_DIVTWO<td>0x2F19</td><td>0x03</td><td>Frequency Synthesizer Divide by 2</td></tr>

<tr><td>FS_DSM0<td>0x2F1B</td><td>0x33</td><td>FS Digital Synthesizer Module Configuration Reg. 0</td></tr>

<tr><td>FS_DVC0<td>0x2F1D</td><td>0x17</td><td>Frequency Synthesizer Divider Chain Configuration ..</td></tr>

<tr><td>FS_PFD<td>0x2F1F</td><td>0x00</td><td>Frequency Synthesizer Phase Frequency Detector Con..</td></tr>

<tr><td>FS_PRE<td>0x2F20</td><td>0x6E</td><td>Frequency Synthesizer Prescaler Configuration</td></tr>

<tr><td>FS_REG_DIV_CML<td>0x2F21</td><td>0x1C</td><td>Frequency Synthesizer Divider Regulator Configurat..</td></tr>

<tr><td>FS_SPARE<td>0x2F22</td><td>0xAC</td><td>Frequency Synthesizer Spare</td></tr>

<tr><td>FS_VCO0<td>0x2F27</td><td>0xB5</td><td>FS Voltage Controlled Oscillator Configuration Reg..</td></tr>

<tr><td>IFAMP<td>0x2F2F</td><td>0x09</td><td>Intermediate Frequency Amplifier Configuration</td></tr>

<tr><td>XOSC5<td>0x2F32</td><td>0x0E</td><td>Crystal Oscillator Configuration Reg. 5</td></tr>

<tr><td>XOSC1<td>0x2F36</td><td>0x03</td><td>Crystal Oscillator Configuration Reg. 1</td></tr>

<tr><td>SERIAL_STATUS<td>0x2F91</td><td>0x08</td><td>Serial Status</td></tr>

</table>

</body><html><html><head>

<style>

body {background-color:#dde;}

caption {font-weight:bold; font-size:16px;margin-left:30px}

th { text-align:left; background-color:#f00; color:#fff}

table { background-color: #eec; font-size:9px;margin:10px}

</style>

</head>

<body><table border=1 cellpadding=5 cellspacing=0>

<caption>CC1200 registers</caption>

<tr><th>Name</th><th>Address</th><th>Value</th>

<th>Description</th></tr><tr><td>IOCFG2<td>0x0001</td><td>0x08</td><td>GPIO2 IO Pin Configuration</td></tr>

<tr><td>IOCFG0<td>0x0003</td><td>0x09</td><td>GPIO0 IO Pin Configuration</td></tr>

<tr><td>SYNC_CFG1<td>0x0008</td><td>0xBF</td><td>Sync Word Detection Configuration Reg. 1</td></tr>

<tr><td>SYNC_CFG0<td>0x0009</td><td>0x23</td><td>Sync Word Detection Configuration Reg. 0</td></tr>

<tr><td>DEVIATION_M<td>0x000A</td><td>0x47</td><td>Frequency Deviation Configuration</td></tr>

<tr><td>MODCFG_DEV_E<td>0x000B</td><td>0x0C</td><td>Modulation Format and Frequency Deviation Configur..</td></tr>

<tr><td>DCFILT_CFG<td>0x000C</td><td>0x4B</td><td>Digital DC Removal Configuration</td></tr>

<tr><td>PREAMBLE_CFG1<td>0x000D</td><td>0x00</td><td>Preamble Length Configuration Reg. 1</td></tr>

<tr><td>PREAMBLE_CFG0<td>0x000E</td><td>0x8A</td><td>Preamble Detection Configuration Reg. 0</td></tr>

<tr><td>IQIC<td>0x000F</td><td>0xD8</td><td>Digital Image Channel Compensation Configuration</td></tr>

<tr><td>CHAN_BW<td>0x0010</td><td>0x08</td><td>Channel Filter Configuration</td></tr>

<tr><td>MDMCFG1<td>0x0011</td><td>0x02</td><td>General Modem Parameter Configuration Reg. 1</td></tr>

<tr><td>MDMCFG0<td>0x0012</td><td>0x05</td><td>General Modem Parameter Configuration Reg. 0</td></tr>

<tr><td>SYMBOL_RATE2<td>0x0013</td><td>0xA4</td><td>Symbol Rate Configuration Exponent and Mantissa [1..</td></tr>

<tr><td>SYMBOL_RATE1<td>0x0014</td><td>0x7A</td><td>Symbol Rate Configuration Mantissa [15:8]</td></tr>

<tr><td>SYMBOL_RATE0<td>0x0015</td><td>0xE1</td><td>Symbol Rate Configuration Mantissa [7:0]</td></tr>

<tr><td>AGC_REF<td>0x0016</td><td>0x2A</td><td>AGC Reference Level Configuration</td></tr>

<tr><td>AGC_CS_THR<td>0x0017</td><td>0x01</td><td>Carrier Sense Threshold Configuration</td></tr>

<tr><td>AGC_CFG3<td>0x0019</td><td>0x11</td><td>Automatic Gain Control Configuration Reg. 3</td></tr>

<tr><td>AGC_CFG1<td>0x001B</td><td>0x12</td><td>Automatic Gain Control Configuration Reg. 1</td></tr>

<tr><td>AGC_CFG0<td>0x001C</td><td>0x80</td><td>Automatic Gain Control Configuration Reg. 0</td></tr>

<tr><td>FIFO_CFG<td>0x001D</td><td>0x00</td><td>FIFO Configuration</td></tr>

<tr><td>FS_CFG<td>0x0020</td><td>0x12</td><td>Frequency Synthesizer Configuration</td></tr>

<tr><td>PKT_CFG2<td>0x0026</td><td>0x01</td><td>Packet Configuration Reg. 2</td></tr>

<tr><td>PKT_CFG1<td>0x0027</td><td>0x00</td><td>Packet Configuration Reg. 1</td></tr>

<tr><td>PKT_CFG0<td>0x0028</td><td>0x20</td><td>Packet Configuration Reg. 0</td></tr>

<tr><td>PKT_LEN<td>0x002E</td><td>0xFF</td><td>Packet Length Configuration</td></tr>

<tr><td>IF_MIX_CFG<td>0x2F00</td><td>0x1C</td><td>IF Mix Configuration</td></tr>

<tr><td>FREQOFF_CFG<td>0x2F01</td><td>0x22</td><td>Frequency Offset Correction Configuration</td></tr>

<tr><td>TOC_CFG<td>0x2F02</td><td>0x03</td><td>Timing Offset Correction Configuration</td></tr>

<tr><td>MDMCFG2<td>0x2F05</td><td>0x02</td><td>General Modem Parameter Configuration Reg. 2</td></tr>

<tr><td>FREQ2<td>0x2F0C</td><td>0x5C</td><td>Frequency Configuration [23:16]</td></tr>

<tr><td>FREQ1<td>0x2F0D</td><td>0x0F</td><td>Frequency Configuration [15:8]</td></tr>

<tr><td>FREQ0<td>0x2F0E</td><td>0x5C</td><td>Frequency Configuration [7:0]</td></tr>

<tr><td>IF_ADC1<td>0x2F10</td><td>0xEE</td><td>Analog to Digital Converter Configuration Reg. 1</td></tr>

<tr><td>IF_ADC0<td>0x2F11</td><td>0x10</td><td>Analog to Digital Converter Configuration Reg. 0</td></tr>

<tr><td>FS_DIG1<td>0x2F12</td><td>0x07</td><td>Frequency Synthesizer Digital Reg. 1</td></tr>

<tr><td>FS_DIG0<td>0x2F13</td><td>0xA5</td><td>Frequency Synthesizer Digital Reg. 0</td></tr>

<tr><td>FS_CAL1<td>0x2F16</td><td>0x40</td><td>Frequency Synthesizer Calibration Reg. 1</td></tr>

<tr><td>FS_CAL0<td>0x2F17</td><td>0x0E</td><td>Frequency Synthesizer Calibration Reg. 0</td></tr>

<tr><td>FS_DIVTWO<td>0x2F19</td><td>0x03</td><td>Frequency Synthesizer Divide by 2</td></tr>

<tr><td>FS_DSM0<td>0x2F1B</td><td>0x33</td><td>FS Digital Synthesizer Module Configuration Reg. 0</td></tr>

<tr><td>FS_DVC0<td>0x2F1D</td><td>0x17</td><td>Frequency Synthesizer Divider Chain Configuration ..</td></tr>

<tr><td>FS_PFD<td>0x2F1F</td><td>0x00</td><td>Frequency Synthesizer Phase Frequency Detector Con..</td></tr>

<tr><td>FS_PRE<td>0x2F20</td><td>0x6E</td><td>Frequency Synthesizer Prescaler Configuration</td></tr>

<tr><td>FS_REG_DIV_CML<td>0x2F21</td><td>0x1C</td><td>Frequency Synthesizer Divider Regulator Configurat..</td></tr>

<tr><td>FS_SPARE<td>0x2F22</td><td>0xAC</td><td>Frequency Synthesizer Spare</td></tr>

<tr><td>FS_VCO0<td>0x2F27</td><td>0xB5</td><td>FS Voltage Controlled Oscillator Configuration Reg..</td></tr>

<tr><td>IFAMP<td>0x2F2F</td><td>0x09</td><td>Intermediate Frequency Amplifier Configuration</td></tr>

<tr><td>XOSC5<td>0x2F32</td><td>0x0E</td><td>Crystal Oscillator Configuration Reg. 5</td></tr>

<tr><td>XOSC1<td>0x2F36</td><td>0x03</td><td>Crystal Oscillator Configuration Reg. 1</td></tr>

<tr><td>SERIAL_STATUS<td>0x2F91</td><td>0x08</td><td>Serial Status</td></tr>

</table>

</body><html>