デルタ・シグマ・アナログ/デジタル・コンバータ(ADC)はデルタ・シグマ変調器とデジタル・フィルタで構成されます。変調器はアナログ入力をデジタル・ビット・ストリームに変換し、一方、デジタル・フィルタはビット・ストリームを、アナログ入力の大きさを表すデータ・ワードに変換します。

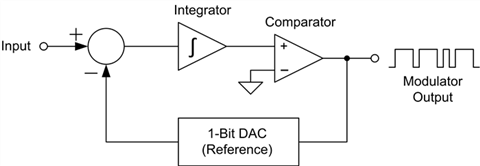

まず、変調器の働きを見ていきます。図1に示す、1次デルタ・シグマ変調器トポロジの非常に基礎的な分析から開始します。

変調器は入力のサンプリング間隔を決定する変調器クロックから動作を開始します。入力サンプルと1ビットDAC間の差を積分することにより、変調ループが始まります。

コンパレータは積分器の値に基づき、次の変調器出力を決定します。1ビットDACはコンパレータの出力状態に応じて、ADCの正負基準電圧に等しい電圧を生成します。変調器出力が1の場合、基準電圧は入力から差し引かれます。変調器出力が0の場合、基準電圧は入力電圧に加えられます。変調器クロックのパルスごとに、変調器が全サイクルを完了し、新しい出力を生成します。

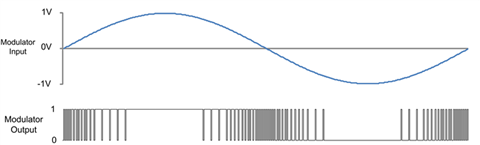

変調器クロックが動作を継続するにつれて、変調器クロックのパルスはそれぞれ別の変調器出力パルスを生成します。結果的に生じる出力ビット・ストリームは、基準電圧に比例する入力電圧を表します。図2は1Vの基準電圧を仮定した場合の、入力正弦波と結果的に生じる変調器出力ビット・ストリームを示しています。

入力が1Vに近づくと、変調器のビット・ストリームは100%の1s密度に近づきます。反対に、入力が-1Vに近づくと、ビット・ストリーム1s密度は0%に近づきます。入力が0Vの場合、1s密度は50%です。従って、基準電圧と負の基準電圧の間の入力電圧は、変調器を「オーバーレンジ」せずに測定可能です。

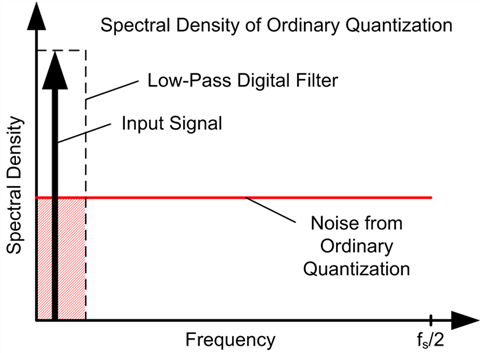

変調器は入力をビット・ストリームに変換することにより、何を実現するのでしょうか?変調器のスペクトル・コンテンツを見ると、以下の図3aに示すように、入力電圧とサンプリングされたデジタル信号の間のエラーは量子化ノイズとしてモデル化されます。単純な量子化により、エラー・スペクトル密度は、DCから2で割ったサンプリング周波数(fS)へのホワイトノイズです。

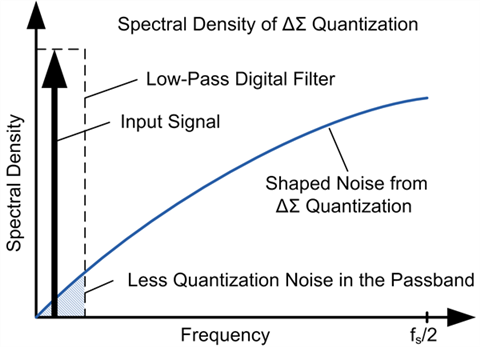

デルタ・シグマ変調の使用により、図3bに示すように、量子化エラー・スペクトル密度は高い周波数に押し上げることにより形成されます。量子化ノイズがデジタル・フィルタのパスバンド外に移動してしまっていることから、ローパス・デジタル・フィルタはより高い分解能で入力信号を維持します。デルタ・シグマ変調により、量子化ノイズの低減と分解能の向上を実現できます。

|

|

| 図3a:通常の量子化からのノイズ | 図3b:デルタ・シグマ量子化からのノイズ |

追加的なフィードフォワード/フィードバック・パスを備えた多次のさまざまな変調器トポロジは、上記の基本的な例に比べ優れたノイズ・シェーピングを実現します。異なるデジタル・フィルタが元の信号を抽出し、測定分解能のより高いADCを高速化します。

この複雑なトポロジを基礎レベルに分解することにより、デルタ・シグマ変調器の動作を理解することができます。変調器は入力信号をサンプリングし、基準電圧と比較し、入力信号の大きさに比例する1sのビット・ストリームを出力します。今後のブログで、測定分解能を向上するために変調器とデジタル・フィルタを組み合わせる方法について解説する予定です。

詳細については以下のリソースもご覧ください。

- TI の広範なデルタ・シグマADC製品ラインナップ

- デルタ・シグマADCの動作Part 1(Bonnie Baker著、Analog Applications Journal)(英語)

- デルタ・シグマADCの動作Part 2(Bonnie Baker著、Analog Applications Journal)(英語)

上記の記事は下記 URL より翻訳転載されました。

*ご質問は E2E 日本語コミュニティにお願い致します。