信号の分解の第9部でも述べたように、データ収集(DAQ)システムにはすべて基準点が必要です。第9部でのその基準点は、出力コードの生成のためにアナログ入力信号と比較される電圧レベルでした。しかし、DAQシステムには別の種類の基準点も必要であり、それは必ずしも電圧に関連したものではありません。

DAQシステム内では、すべてのコンポーネントが同期して動作できるようにする時間的基準としてクロックが使用されます。A/Dコンバータ(ADC)に関して言えば、クロックが正確で安定していることによって、ホストがADCにコマンドを送り、ADCがホストからコマンドを受け取る際に、それらが正しい順序で、データの破損なしで行われることが保証されます。さらに重要なのは、システムのクロック信号により、ユーザーがいつでも必要なときに入力をサンプリングし、データを送信できることで、システム全体が意図したとおりに動作することです。

クロックのことをデジタル入力信号だと考えているかもしれませんが、クロックは高精度DAQシステムのアナログ性能に影響する可能性があります。クロックが高精度ADCにどう影響するかを深く理解するために、クロック信号に関連する以下のトピックを取り上げます。

- クロック・ジッタ

- クロック相互変調

- クロックに関するプリント基板(PCB)レイアウトのベスト・プラクティス

クロック・ジッタ

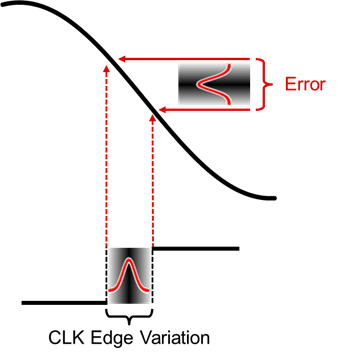

ADCのサンプリング周期が完全に一定であることを期待しているかもしれませんが、理想とのずれは幾分かはあります。「クロック・ジッタ」とは、ある周期から次の周期までのクロック波形のエッジの変動量を意味します。すべてのADCがクロック・エッジを使ってサンプリング点をコントロールするので、クロック・エッジの変動によりサンプリングされるものにずれが生じます。このずれの結果、サンプリング周波数が一定でなくなり、新たなノイズ源として変換結果に表れます。

このシリーズでこれまで取り上げたほとんどのノイズ源と同様に、クロック・ジッタもランダムに発生し、ガウス分布に従います。そのため、サンプリングの不確定性誤差もガウス分布であり、熱ノイズと同じ振る舞いになります。最終的に、ADC性能に与えるクロック・ジッタの影響により、主にADCのノイズ・フロアが上昇し、シグナル・チェーンの総熱ノイズの増加につながります。図1は、正弦波入力信号上にクロック・ジッタにより生じたサンプリング・エッジの変動を表したものです。

図1. ジッタによるサンプリング・エッジの変動を示すクロック信号

熱ノイズがどの程度増加するかは、入力信号のスルー・レートとクロック源のクロック・ジッタの量により変わります。ADCの信号対雑音比(SNR)の理論的な上限は、式1を用いて計算できます。

SNRUpper Limit=-20×log10(2×π×fIN×tJITTER) (1)

ここで、fINは入力信号周波数、tJITTERはクロック源のジッタの仕様です。信号の周波数成分が高くなると、入力信号のスルー・レートが上昇し、クロック・ジッタによりSNRが悪化することが予想できます。

デルタ-シグマADCのようなオーバーサンプリング・コンバータの重要な利点の1つに、オーバーサンプリング比(OSR)が高いと、理想的なSNRが改善することがあります。オーバーサンプリングにより、ある決まった期間の複数の変換から平均を取るので、クロック・ジッタで生じるサンプリング変動もいくらか平均化されます。式2を使って、オーバーサンプリングにより改善するSNRの量を定量化します。式2は単に、デルタ-シグマADCのOSRに依存する項を式1に追加したものです。

SNRUpper Limit(Oversampling)=-20×log10×(2×π×fIN× tJITTER)+10×log10×(OSR) (2)

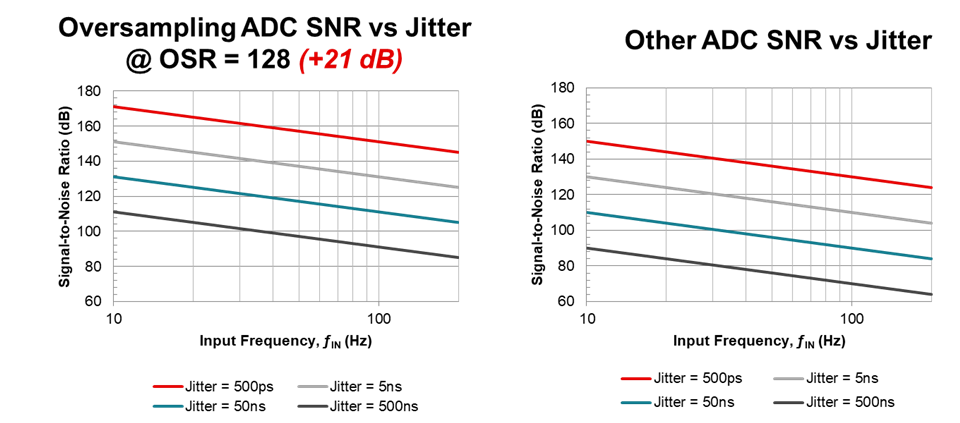

オーバーサンプリングADCとオーバーサンプリングでないADCの性能の違いを図で示すために、図2に入力信号周波数とジッタの関数として式1と式2をプロットしました。それぞれのプロットには、クロック・ジッタ仕様の異なる4つのグラフが含まれます(0.5ns、5ns、50ns、500ns)。図2aがオーバーサンプリングADCのSNR、図2bはオーバーサンプリング・アーキテクチャを持たないADCです。

(a) (b)

図2. オーバーサンプリングADC (a)と、そうでないADC (b)のSNRプロット

オーバーサンプリングの恩恵があるので、図2aの4つのプロットでは、それに相当する図2bのジッタ仕様のグラフと比べて、21dBの改善が見られます。しかし、プロットは両方とも、入力信号周波数を上げるかクロック・ジッタの量が増えるとSNRが低下するという、同じ現象を表しています。したがって、SNR目標が高いアプリケーションでは、ジッタを最小限に抑えるための高価でパワーのあるクロック・ソリューションが必要になることがあります。

例えば、TIの512kSPS、24ビット・デルタ-シグマADC『ADS127L01』用評価モジュール(EVM)では、Abracon社の低ジッタ発振器ASEMB-16.000MHZ-XY-Tを使用しています。この発振器の標準期間ジッタ仕様は5psと、図2でプロットしたどのジッタ仕様よりもかなり低いものです。しかし、コストと性能のトレードオフを考慮すると、本当にこの発振器が必要なのか、高性能すぎるのではないかと悩むかもしれません。

この問いに答えるために、表1で『ADS127L01』のデータシートのノイズ仕様を比較します。「ワイドバンド1」デジタル・フ���ルタ設定を使用し、5psと500psのクロック・ジッタに対するSNR上限を計算しました。SNR上限の計算には、デジタル・フィルタの通過帯域周波数を、最大入力信号周波数を表す「fIN」として使用します。この周波数のときに、クロック・ジッタの影響が最も顕著に現れます。

tJITTER = 5psのときは、��出したすべて���SNR値がADCのデータシートのSNR仕様��超えています(緑で���りつぶされたセル)。このクロック源を使った場合、クロック・ジッタからのノイズはシステムの主要なノイズ源にならない、と想定しても大丈夫でしょう。これを、ADCのSNR仕様を下回るSNR値を示す、赤で塗りつぶされたセルと比べてみましょう。これらはすべてtJITTER = 500psの場合です。この場合、信号帯域幅をフ��に使用するときにADCが達成できるSNRは、実際にクロック・ジッタのノイズにより制限されることになります。

表1. 5psと500psのクロック・ジッタについて、TIの『ADS127L01』「ワイドバンド1」フィルタSNRとSNRUpper Limitの比較

|

動作 モード |

データ・ |

OSR |

通過帯域 (kHz) |

ADC SNR (dB) (データシート) |

SNRUpper Limit (dB) (tJITTER = 5 ps) |

SNRUpper Limit (dB) (tJITTER = 500 ps) |

|

高分解能 |

512,000 |

32 |

230.4 |

103.7 |

117.9 |

77.9 |

|

256,000 |

64 |

115.2 |

107.3 |

126.9 |

86.9 |

|

|

128,000 |

128 |

57.6 |

110.4 |

135.9 |

95.9 |

|

|

64,000 |

256 |

28.8 |

113.4 |

145.0 |

105.0 |

|

|

低消費 電力 |

256,000 |

32 |

115.2 |

103.9 |

123.9 |

83.9 |

|

128,000 |

64 |

57.6 |

107.6 |

132.9 |

92.9 |

|

|

64,000 |

128 |

28.8 |

110.7 |

141.9 |

101.9 |

|

|

32,000 |

256 |

14.4 |

113.7 |

151.0 |

111.0 |

|

|

超低 消費電力 |

128,000 |

32 |

57.6 |

104.1 |

129.9 |

89.9 |

|

64,000 |

64 |

28.8 |

107.8 |

138.9 |

98.9 |

|

|

32,000 |

128 |

14.4 |

110.9 |

148.0 |

108.0 |

|

|

16,000 |

256 |

7.2 |

113.9 |

157.0 |

117.0 |

表1と図2からわかるもう1つの重要な点は、OSRの上昇(ADCの出力データ・レートを落とすのと同じ意味)によりSNR性能がさらに向上することです。一般に、低い出力データ・レートに対応できるシステムは、動きの遅い入力信号を測定していることになります。これらのシステムでは、事実上クロック・エッジのわずかな変動に「気付かない」ので、ジッタによるノイズが少ないように見えます。

最後に、クロック・ジッタで生じるノイズを低減するもう1つの方法は、例えば『ADS131A04』など、内蔵のクロック分周回路を使用して変調器のサンプリング・クロックを生成するADCを選ぶことです。クロック分周回路は、2つの入力クロック・エッジのうちの1つ(通常は立ち上がりエッジ)でのみ働き、元の入力クロック周波数の半分以下の出力クロック周波数を生成します。当然ながら、ジッタによっては両方の入力クロック・エッジで発生すると考えられるため、クロックを半分に分割すると、事実上出力クロックのジッタを低減することになります。続けて何回も入力クロックを分周すると、ADCに与える入力クロックのジッタの影響はさらに低くなります。

クロック相互変調

クロック相互変調によっても、クロック源がADCのノイズ特性に影響してシステムのノイズが増加します。ほとんどすべてのDAQシステムに、クロック入力が必要なスイッチング部品が多数含まれていますが、場合によっては、別々のクロック源から生成される異なる入力周波数のクロック入力が必要になるかもしれません。

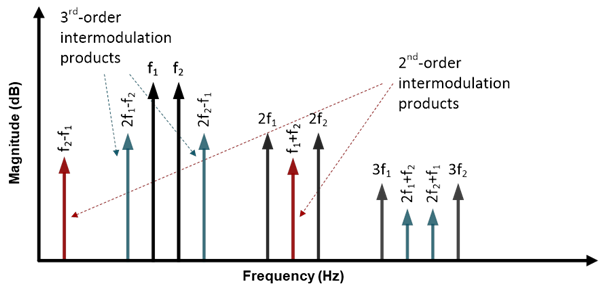

これらのクロック源が個別の部品で非同期の場合は、お互いに結合して周波数スペクトラムにトーンが生成される可能性があります。2つのクロック源の周波数をF1、F2として、これらの基本周波数の差または和から相互変調トーンが発生します。図3に示すこれらのトーンは、2次相互変調歪みと呼ばれます。

図3. 非同期クロック源による相互変調歪み

さらに、基本周波数の和または差と、その高調波を含めた別の相互変調歪みからも、より高次のトーンが発生します。対象の信号帯域幅を超えたところにこれらのトーンが存在したとしても、ADC通過帯域に折り返して、SNRや全高調波歪みなどのAC仕様を悪化させる可能性があります。

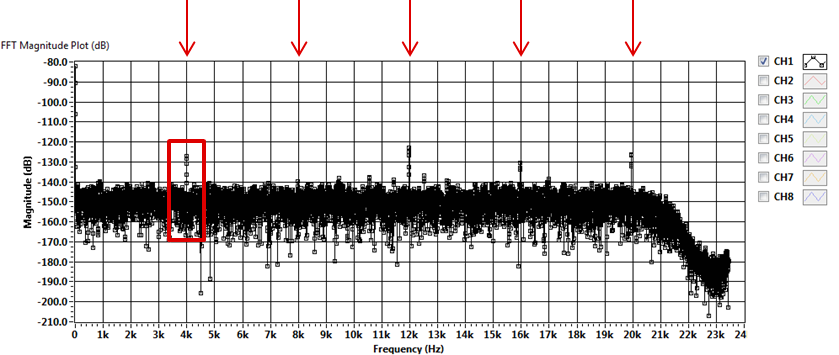

図4の高速フーリエ変換(FFT)には、この相互変調の影��が見られます。入力を短絡したADC(0Vの差動入力)を使用し、プロセッサの���ロックは12MHzに設定して、ADCの変調器のクロックを11.996MHzに下げました。これにより4kHzの差が生じます。

図4. 4kHzの倍数に相互変調トーンが現れるFFT

プロセッサとADCのクロックの差により、4kHzで周波数スペクトラムに2次相互変調トーンが現れ、4kHzの倍数に高調波も見られます。このことは、相互変調歪みがADCの通過帯域に直接入ってノイズの要因になりうることを示しています。

この影響を軽減するために、広帯域アプリケーションでは、システムで使用する全周波数を1つのクロック源から生成し、それらすべての同期を保証することがよく行われます。他にも、対象の信号帯域幅内でトーンが生成されるおそれが最も少ないクロック周波数とサンプリング・レートを選ぶ方法もあります。

クロックに関するPCBレイアウトのベスト・プラクティス

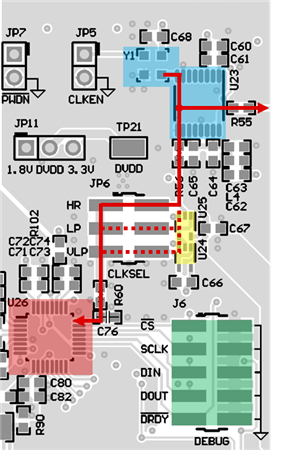

クロック源に関してPCBレイアウトを設計するときは、クロック信号をできるだけクリーンに保つことに注意を払ってください。クロック信号はデジタル入力だと見なされていますが、これも重要なアナログ信号の1つと考えて扱ってください。配線のインピーダンスが最小限になるようにし、シリアル・ペリフェラル・インターフェイス(SPI)信号や他のノイズの多い回路からなるべく離れるように配線し、PCBフットプリントには反射またはオーバーシュートに対処する直列抵抗とシャント・コンデンサのための余裕を考慮してください。図5は、『ADS127L01EVM』のクロック・レイアウトの例を示したものです。

図5. クロック・レイアウトの例

図5の赤いラインは、クロック源からADC(赤で塗られたU26)までの配線を示しています。クロック源(Y1)から出るクロックのパスは、クロック・ファンアウト・バッファ(U23)に入ります(図5の右上に青で示す部分)。クロック・ファンアウト・バッファは、元の入力クロック周波数とまったく同じコピーを2つ生成します。1つはADCを、もう1つは(R55を通って)マイクロコントローラを駆動するためのものです。

ADCに向かうクロック信号は、続いて、クロック・バッファ出力と直列に接続された43Ωの小さな抵抗(R56)を通過します。これは反射を抑制するためのものです。次にクロック信号はジャンパ(JP6)に接続します。このジャンパで、3つのADCクロック周波数のうち1つが選択されます。他の2つのクロック周波数は、2つのDフリップフロップ(図5で黄色で示すU24とU25)で生成されます。これらの部品がクロック・バッファ出力を分周し、「低消費電力」(LP)モードと「超低消費電力」(VLP)モードという2つのモード用のクロックを生成します。3つのモードはすべて、元のクロック源とも同期しています。図5では、赤の実線は「高分解能」(HR)モードを選んだラインを通過します。

ジャンパの後に、選択されたクロック信号は、別の抵抗(R60)とシャント・コンデンサ(C76)を通過してからADCのクロック・ピンに到達します。このパスは、なるべくまっすぐで最短になるようにしてください。SPIインターフェイス信号(緑の部分)も、ADCに到達するまで、クロック入力からできるだけ離すようにします。

最高の性能を得るためのクロックに関するさらなるヒント

ここで述べたクロック・レイアウトのガイドラインに従っても、まだクロックのせいでADC性能が悪化している疑いがある場合は、クロックに関連する以下の問題点も調べてみてください。

- ADC入力でのクロック信号の品質。ADCのクロック入力ピンのクロック信号に過剰なオーバーシュートやリンギングが見られる場合は、小さな直列抵抗とシャント・コンデンサ(図5のR60とC76)を追加するかサイズを大きくすることで、クロック・エッジのスルー・レートを改善する必要があるでしょう。これらの部品を追加することで、事実上クロック入力にローパス・フィルタが加えられますが、基本クロック周波数は保たれます。

また、クロック・エッジに「段差」のようなものが見られるかもしれません。これは、クロック信号が配線を通って高インピーダンスの入力へ至る際の反射により発生します。このようなクロック反射の抑制には、直列抵抗が有効でしょう。

- ADCの電源ピン。ADCのDVDD入力とクロック源またはクロック・バッファは、ともに同じデジタル電源を使用する場合があるため、これらのピンに大きな過渡事象がないかチェックします。過渡事象は電流の急な需要が原因で起こり、これを抑えるにはデカップリング・コンデンサを追加する必要があるかもしれません。ただし、デカップリング・コンデンサのサイズを選ぶ際には注意が必要です。デカップリング・コンデンサが小さいとインダクタンスが低くなり、必要な電流を素早く供給することができます。一方でデカップリング・コンデンサが大きいと、必要な大容量の電荷を蓄えることができ、電源レールのノイズをフィルタリングするのに役立ちます。ノイズが少なく安定したデジタル電源を維持するには、大型と小型のデカップリング・コンデンサを組み合わせる必要があるかもしれせん。

過渡事象がADC出力にカップリングするのを抑えるもう1つの方法は、ADCのデジタル電源ピンとクロック源またはクロック・バッファの電源ピンとの間に小さいフェライト・ビーズを配置することです。

- グランド・プレーンを分割する。PCBサイズの制約のせいで感度の高いアナログ回路からクロック回路を離すことができない場合は、クロック電流のリターン・パスを分離するために部分的にグランドを分割するのが有効かもしれません。ただし、ADCのアナログ部とデジタル部のグランド電位差が顕著にならないように、常にグランド・プレーンの両サイドをデバイスのできるだけ近くに接続してください。

この記事で推奨した技法や手順に従えば、クロック関連でよくある問題をほとんど防ぎ、クロック源がシグナル・チェーンのノイズ要因にならないようにできるでしょう。

次回、「信号の分解」シリーズの第11部では、高精度ADCに与える電源の影響について説明します。

著者紹介

Bryan Lizon(Texas Instruments)

テキサス・インスツルメンツ 高精度ADC製品プロダクト・マーケティング・エンジニア

※すべての登録商標および商標はそれぞれの所有者に帰属します。

※ご質問はE2E Support Forumにお願い致します。