ラフール・プラカシュ(Rahul Prakash)、クナル・ガンディー(Kunal Gandhi)/Texas Instruments

より多くの産業用システムが、より高い精度を必要としています。これまで、高精度のシグナル・チェーン部品の開発を促進してきたのは主としてテスト/計測機器でしたが、現在、この傾向はファクトリ・オートメーション、光ネットワーキングや医療用機器まで広がっています。ATE(自動テスト装置)、DAQ(データ収集)や高性能オシロスコープ製品は、最も高精度のシグナル・チェーンが必要です。

高精度D/Aコンバータは、このようなシグナル・チェーンに必須の部品であり、高精度信号に最も大きな影響を与える構成要素でもあります。通常、高精度D/Aコンバータは、ゲインとオフセットの微調整や、その他の非直線性を最小にするために使います。したがって高精度D/Aコンバータは信号の較正を行うことで、信号の精度を向上することになります。本稿では、D/Aコンバータに使われる2つのアーキテクチャ、R2RラダーとストリングDACについて説明します。さらに、それらのアーキテクチャで精度の向上に役立つ手法を検討します。

高精度D/Aコンバータの精度

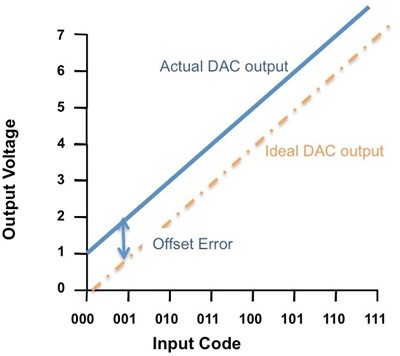

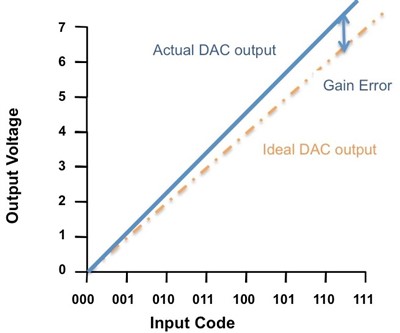

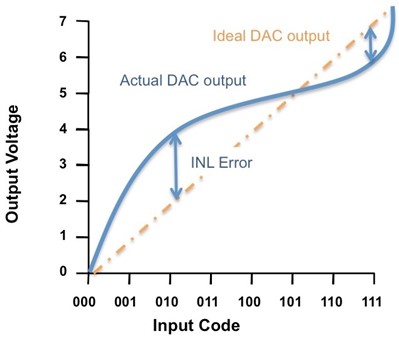

高精度D/Aコンバータを含むアナログICには、数多くの非理想的特性が存在します。高精度D/AコンバータのDC(直流)誤差の主な原因には、OE(オフセット誤差)、GE(ゲイン誤差)やINL(積分非直線性)があります。オフセット誤差は、図1に示すように、直線動作領域の伝達関数からの、実際の出力値のずれの程度を表します。ゲイン誤差は、図2のように、理想的な伝達関数の傾斜からの偏差を、最下位ビット(1LSB)で表したものです。 INLはD/Aコンバータの理想的な出力値と、実際の出力値の間のずれを表します。例として、図3に、簡単な3ビットD/Aコンバータの実際の出力と理想出力の様子を示します。

図 1: 簡単な3ビットD/Aコンバータのオフセット誤差

図2: 簡単な3ビットD/Aコンバータのゲイン誤差

図3: 簡単な3ビット D/Aコンバータの積分非直線性特性

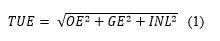

D/Aコンバータの精度の評価には、これら3種類の誤差のすべてが含まれなければなりません。D/Aコンバータの精度を定量的に表すために、しばしば、総合未調整誤差(TUE)という言葉が使われます。これら3種類の誤差は互いに相関していないことから、TUEは式(1)に示すように、これらのニ乗和の平方根(RSS)から計算されます。

オフセット誤差とゲイン誤差は、しばしば、簡単な較正手法を使って、システム上で較正されます。一方、INL誤差の補正には、多くのプログラム・コードを使った、より 強力な較正手法が必要です。これはソフトウェアにとって無視できない負荷となるとともに、複数の係数を記憶するために、より大きなメモリ容量が必要となります。したがって精度の向上には、D/AコンバータのINL誤差を最小にすることが最も重要になります。

D/AコンバータのアーキテクチャとINL誤差の関係

最も主要なD/AコンバータのアーキテクチャはR(抵抗)ストリング、またはR2Rラダーを使ったトポロジです。これらの方式のD/Aコンバータで、最も大きなINL誤差の要因となるのは、ラダーやストリングを構成する抵抗のミスマッチです。多くのアナログプロセスは、ラダーやストリングを設計するための高精度抵抗を含みます。より高い精度への要求が増加するにつれて、高精度抵抗では不十分になりました。この問題に対応し、抵抗のミスマッチの影響を補正するために、追加の設計、レイアウトやトリミングなどの追加手法が使われるようになりました。D/Aコンバータの総合的な精度向上に有効な手法は、R2RラダーとRストリングのどちらのアーキテクチャが選択されているかによって異なります。

Rストリング

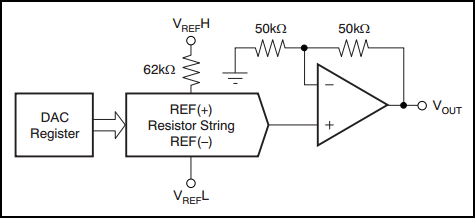

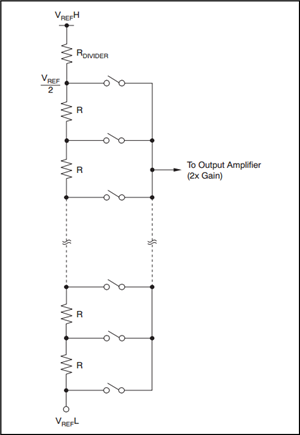

通常、Rストリング方式のD/Aコンバータは、その名前が示す通り、リファレンス電位とグラウンドとの間に抵抗ストリングを接続し、デジタル入力に対応する電圧を発生します。複数のスイッチを介して、この電圧を出力バッファに接続します。出力バッファは、D/Aコンバータにドライブ能力を提供します。例として、図4と図5 にRストリング・アーキテクチャのD/Aコンバータを示します。

図4: D/Aコンバータの内部アーキテクチャの例

図5: D/Aコンバータの R ストリング・アーキテクチャの例

16ビット D/AコンバータのRストリングには、2^16個(2の16乗 = 65,536個)の抵抗が必要です。通常、RストリングはMSB(最上位ビット)のストリングと、LSB(最下位ビット)のストリングとして分割されます。それにもかかわらず、INL誤差を最小限にするためには、これらすべての抵抗は、他の抵抗とマッチしていることが必要です。革新的なレイアウト手法のほか、適切なサイズの選択によって、これらの抵抗のマッチングを向上させます。

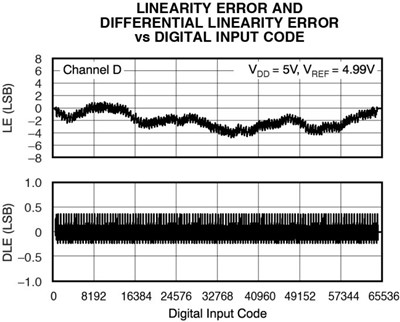

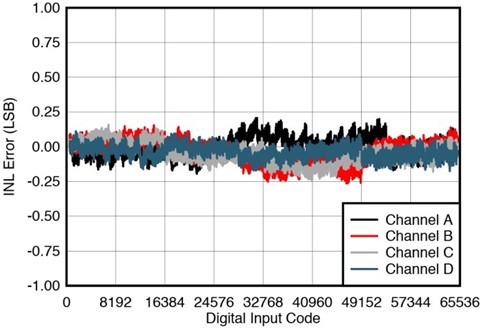

図6 にDAC 8554などのRストリング方式のD/Aコンバータのデジタル入力コードに対するINL特性を示します。

図 6: D/Aコンバータ直線性誤差(LEまたはINL)��� デジタル入力コード

R2Rラダー

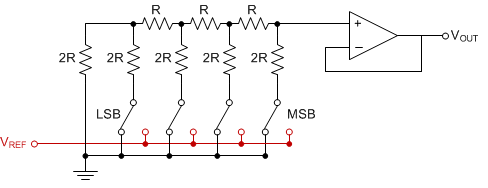

R2Rラダー方式のD/AコンバータはNビット分解能のD/Aコンバータを最も簡単な形で実装できます。R2RラダーのD/Aコンバータの最も簡単な実装型式はN個の2R抵抗レグと、それらをVREF(リファレンス電位)とREFL(グラウンド電位)に切り換えるスイッチ、1個の2R終端抵抗と、 スイッチ付きの2Rレグの間を接続する(N-1)個の R抵抗で構成されています。Nビット分解能のR2Rラダーを構成するには、 (3N+1)ユニットのR抵抗が必要です。出力バッファは、必要な負荷ドライブ能力を提供します。このアーキテクチャから明かなことは、このバイナリ重み付きR2Rラダー回路は、分解能1ビットにつき1個のR2Rレグで構成でき、同等のRストリング方式のD/Aコンバータと比較して、抵抗の数を大幅に少なくできるということです。図7 に4ビットのR2Rラダー方式のD/Aコンバータの基本回路を示します。

図 7: R2R ラダー方式のD/Aコンバータの基本回路

R2R 方式のD/Aコンバータの分解能は、回路内の2R抵抗レグの個数で決まります。一方、D/Aコンバータの精度は、抵抗のマッチングによって決まります。回路のLSB側の抵抗レグのミスマッチが精度に与える影響は低く、逆にMSB側になるほどほど、レグのミスマッチは大きな影響を与えるようになります。抵抗レグのマッチング感度の影響は、LSB側からMSB側に向かって、抵抗レグ1段あたり2倍になります。

トリミングによって精度を向上

図8に、代表的なR2Rラダー方式の16ビットD/Aコンバータを示します。MSB側の数ビットはセグメント化(サーモメトリック・デコーディド)されていることに注意してください。R2Rラダー方式のD/Aコンバータのほとんどが、この方式を採用しています。

図8: R2Rラダー方式のD/Aコンバータの回路

R ストリングとR2Rラダーの各アーキテクチャで精度をトリミングする場合、各抵抗の絶対値を調整します。前に述べたように、高精度を実現する上で最も大きな問題となるのはINL誤差であり、これを調整することは最も実現性の高い選択肢です。Rストリング型のD/Aコンバータは、非常に多くの抵抗で構成されていることから、トリミングは高価になります。R2Rラダー型では調整する抵抗の数が大幅に少ないことから、この問題が克服されます。

R2Rラダー型D/Aコンバータのトリムはトリムが必要な最初のLSBビットから始めます。

データビットS0(LSB)からS15(MSB)を持つ16bitDACにおいて、最初にトリムされるビットがS5と仮定します。トリムルーチンは隣接するコード32と33の間のエラーを見ることから始まります。理想的には隣接コード間の電圧変化は1LSBです。

トリムは双方向であると仮定します、S5のエラーを初期エラーに応じて上方向または下方向に調整します。

S5のトリムが完了したら、S5以上の(S6, S7, 等々)ビットについて、全てのメジャーキャリーエラーの差分を加えてください。MSBメジャーキャリー・ビットコードに至るまで、この手順を続けてください。もし、サーモメトリック・デコーデットされたMSBがあれば、手順が僅かに変化します。その場合は、サーモニック・デコーデットされたメジャーキャリーを、下位から上位の順にトリムします。トリムの終わりでDACは、16bitモノトニシティを示すだけでなく、1LSB以下のINLを達成します。

例として、R2Rラダー型D/Aコンバータ(DAC 80004)のINLを図9に示します。

図 9: DAC 80004 D/Aコンバータ のデジタル入力コードに対する直線性誤差特性

まとめ

高精度D/Aコンバータ製品は、高精度シグナル・チェーン内で主要な地位を占めています。高精度が必要なアプリケーションでは、必要な要件を満足する、適正なD/Aコンバータの選択を検討することが必要です。DAC 8554をはじめとしたRストリング方式のD/Aコンバータ製品は、汎用アプリケーション向けに価値ある選択肢を提供しますが、1LSBのINLという高精度が必要な場合は、基準を満足しません。高精度を要求するアプリケーション向けには、それらの代わりにDAC 80004をはじめとしたR2Rラダー方式のD/Aコンバータ製品が適しています。R2Rラダー方式は、1LSB INL未満の超高精度を実現するための実用的なトリミングの選択肢を提供できるからです。

著者紹介

ラフール・プラカシュ(Rahul Prakash)

TI 高精度アナログ・データ・コンバータ ・グループ プロダクト・ディファイナ

数々の先端テクノロジー専門誌にアナログ回路設計技術に関する記事を執筆、およびカンファレンスにおいて講演を担当。アナログ回路設計と技術に関して3つのアメリカ特許を保有。テキサス大学ダラス校にて理学修士号取得(電気工学、マイクロ・エレクトロニクス専攻)

クナル・ガンディー(Kunal Gandhi)

TI 高精度アナログ・データ・コンバータ・グループ プロダクト・マーケティング・エンジニア

7年間、ミックスド・シグナル設計エンジニアとして従事し、現職に至る。

南カルフォニア大学に理学修士(電気工学)およびテキサス大学オースティン校にて経営学修士(MBA)取得

参考資料

- TI Analog Wire参照(英語)

- OE、GEおよびINLパラメータについて:「D/Aコンバータ の基本:D/Aコンバータの精度」

- 抵抗ストリング・アーキテクチャについて:「D/Aコンバータ の基本:ストリング・セオリ」

- R2Rラダー・アーキテクチャについて:「D/Aコンバータ の基本:抵抗ラダー」

- 高精度D/Aコンバータのアプリケーション:「TI デザイン-高精度」、「リファレンス・デザイン・ライブラリ」からダウンロード

- 初心者から上級設計者までの技術情報:「高精度D/Aコンバータ・ラーニング・センター」

- 高精度D/Aコンバータ・アーキテクチャのトレーニング・シリーズ・ビデオ「高精度D/Aコンバータ講座」(英語)

- データシート:『DAC 8554』、『DAC 80004』

*ご質問は E2E 日本語コミュニティにお願い致します。