スタンバイ電力は、気が付かないうちに消費されることから、バンパイア(夜のうちにこっそり人の血を吸う)電力、またはリーク電力とも呼ばれ、システム内における電力損失の主要な原因の 1 つになっています。 システムの電源がオフになっているときは、電力消費はゼロであると考えがちです。しかし実際は、電源がオフになっている間でも、コンセントや電力供給源に接続されている場合はアプライアンスの一部は引き続き動作しており、貴重な電力を消費しています。

スタンバイ・モードで消費される電力への対処は、電力の厳格な試験手順について定義した ISO 62310 のような規格が導入されて以来、非常に難しくなりました。 これらの厳酷な試験手順と要件が原因で、アプライアンスがこれらの規格を満たすのが困難になっています。

アプライアンスの現時点での実装では、マイコンを活用して電力を管理していますが、もちろんマイコン自体も動作するために電力を消費します。 産業用設計にとっては過酷な話ですが、マイコン自体も、漏れ電力を排除する目的でシステムを設計することを困難にする要因です。 不要なコンポーネントの使用を排除する方法でシステムを設計すると、この問題を容易に解決できます。DC/DC コンバータはシステム・プロセッサやシステムの他のブロックに電力を供給するために必要ですが、スタンバイ・モードを有効にした場合は、これらの DC/DC コンバータをオフに切り替える必要があります。 設計者は統合型パワー・マネージメント IC(PMIC)ソリューションを使用することで、DC/DC コンバータを制御するためのパワー・シーケンスを格納している内蔵メモリを活用し、これらのコンバータの電力遷移を制御できるようになります。

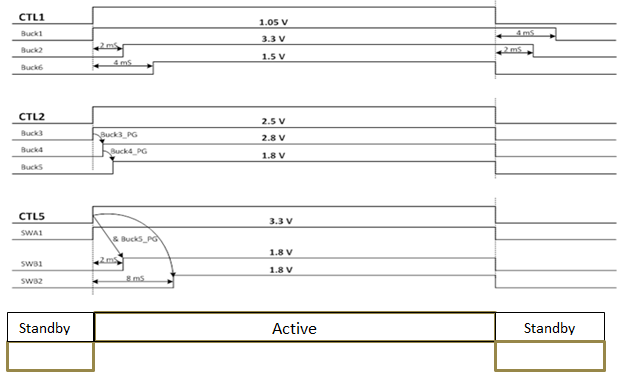

図 1: 電力状態遷移用の制御ピン

図 1 に、システム内にあるこれらのピンを使用して、システムのスタンバイ状態とアクティブ状態を遷移する方法を示します。 これらの制御ピン CTL1、CTL2、CLTL5 はプロセッサの常時オン・ロジックから信号を受信して、アプライアンスをスタンバイ・モードに切り替えます。その結果、マイコンのような 2 次的なドライバがこれらのピンを駆動する必要性が低下します。 すべての電源は、パワー・グッド・タイマのタイムアウト期間に達する前に、ユーザー定義のシーケンスアップ・スレッショルドを上回る必要があります。 いずれかの電源がオンへの正常な切り替えに失敗した場合、シーケンス障害が発生し、制御対象の電源すべてがシャットダウンされます。 すべての電源がそれぞれのシーケンスアップ・スレッショルドに達した時点で、電源モニタが開始されます。 制御対象の電源は、ユーザーが構成した順序で複数のレールをシーケンスアップし、その後、レール間の遅延が内蔵のワンタイム・プログラマブル・メモリに保存されます。 この結果、システムを低消費電力モードに切り替える目的でポイント・オブ・ロード電源に対してコマンドを発行する外部マイコンをシステム内に搭載する必要がなくなります。

PMIC を使用すると、個別のポイント・オブ・ロード・ソリューションを使用するパワー・シーケンスを制御するソフトウェアを構成する際に、ユーザーの時間と労力を節減できます。 通常、電力を節約するために、プロセッサがソフトウェア・コマンドを電源に送信して、スタンバイ状態にある電源をシャットダウンする必要があります。 コマンドはソフトウェア設計者によってプログラミングされ、プロセッサ内にロードされます。 一方、PMIC を使用する場合は、ソフトウェア設計者がこのようなコマンドを記述する必要はありません。これらのコマンドはすでに PMIC 内に格納された状態で出荷されているので、ソフトウェア設計者の時間を節減できます。

ここまでで、PMIC を使用してシステム内の冗長なデバイスを不要にし、PMIC のメモリ内に格納されているプログラミングを使用してスタンバイ・モードの間はコンポーネントを最大限オフに保つ方法を紹介しました。 この方法を採用すると、スタンバイ・モードで実現可能な最小の消費電力を達成し、その結果、バンパイア電力を削減することができます。

スタンバイ電力の目標達成のために是非PMICを活用ください。

その他のリソース:

- TI の包括的な PMIC 製品ラインアップをご確認ください。