多くの産業用および企業用アプリケーションでは、絶縁型電源が必要になることがよくあります。そのような電源を設計する場合は、帰還制御用のフォトカップラを使用する必要があり、新たなレベルの複雑さが加わることになります。TIのLM 5017/8/9およびLM 5160一定オン時間(COT)同期降圧レギュレータ・ファミリは、固有の機能によってフライバック・トポロジでの使用が可能であり、これによってフォトカップラが不要になるため、設計上の複雑さや、BOMコスト、プリント基板(PCB)のコストを削減できます。

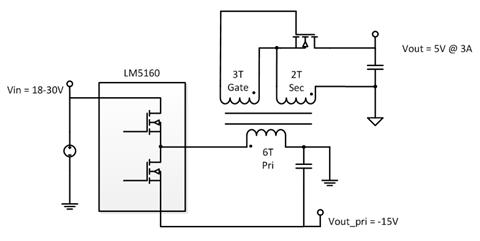

従来のFly-Buckでは絶縁された出力の整流にダイオードを使用していますが、この方法では電流の増加に伴い出力レギュレーション性能が低下し、効率と熱特性の悪化につながります。効率とレギュレーションを許容できるレベルに維持しながら電流の供給量を最大化する方法の1つとして、同期整流器を使用する方法があります。TI Designsの「LM 5160レギュレータを使用した15W絶縁型、セルフ・ドライブ、同期整流、反転Fly-Buckboostリファレンス・デザイン」は、3Aの連続電流を供給できる5V出力を生成するために、LM 5160レギュレータをフライバックとして使用した一例です。このデザインでは、自己駆動巻線を使用して同期整流器のゲートを駆動しています。図1に、反転型昇降圧構成として構成した1次側を示しますが、この理由については後で詳しく説明します。

図1. セルフ・ドライブのブロック図

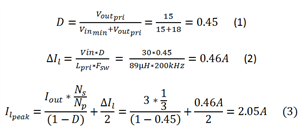

負荷レギュレーションは、1-D周期中にエネルギーが2次側に伝達された結果として、その1-D周期が50%を下回った場合に影響を受けることがあります。1-D周期が減少すると、1-D周期中の1次側のピーク電流は、与えられた負荷に対して大幅に増加します。その結果、ピーク電流の増加により、磁化インダクタンスやリーク・インダクタンスに分散される1次側の電圧が増加するため、負荷レギュレーションが大きな影響を受けます。このことから、フライバックを設計する際は、1-D周期を50%より大きくするよう推奨します。また、LM 5160のピーク電流制限は、特定の巻線比が選択された電流制限に入ることなく3Aの要件を満たすために、最小2.125Aまで(通常は2.5A)下げることができます。このデザインでは、3対1の降圧比を持つVersa-Pacトランスを使用しています。式1と式2に、Vinminでのピーク・インダクタ電流を示します。

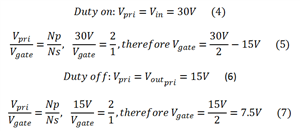

オフ時間中に同期MOSFETを駆動するため、9巻線をトランスに実装して2対1の巻線比を実現しています。式4~7に、Vinmaxでのデューティ・オンおよびデューティ・オフ時の同期FETのVgs電圧を示します。

図2. 最大VinでのVgs

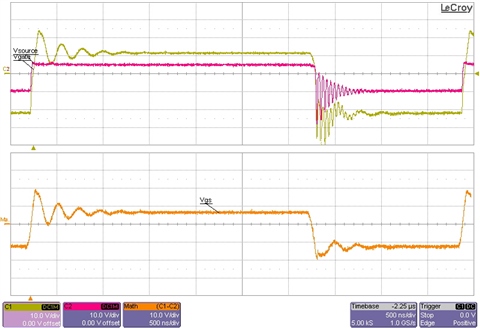

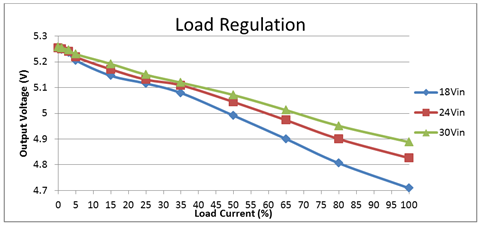

トランスのリーク・インダクタンス、DC抵抗(DCR)、整流器の順方向電圧降下は、フライバック出力レギュレーションに影響する要素です。図3に示すとおり、このデザインでは、同期整流器を使用することで、Vinと負荷の範囲全体にわたって±5%のレギュレーションを実現できます。

図3. Vin範囲全体での負荷レギュレーション

ダイオード整流器を使用した場合、無負荷では、2次側での電圧スパイクにより2次側出力電圧がピーク充電される可能性があります。この同期手法では、無負荷でのレギュレーション用にプリロード抵抗やツェナー・クランプを使用する必要もありません。

Versa-Pacに比べてリーク・インダクタンスとDCRが低い専用のトランスを作成することで、レギュレーションと効率をさらに向上させることができます。また、専用の同期巻線を1次側の巻線と密結合することにより、スイッチング・スパイクが低減し、同期MOSFETのゲート・ソース間最大電圧定格を超える心配がなくなります。

その他のリソース

上記の記事は下記 URL より翻訳転載されました。

*ご質問は E2E 日本語コミュニティにお願い致します。