スイッチング電源のテストは数多くの異なるテストで構成されていますが、その1つに出力電圧のピーク・ツー・ピーク・リップルのテストがあります。出力電圧リップルとは、直流電流(DC)出力電圧の交流電流(AC)成分です。この成分は、出力コンデンサの等価直列抵抗(ESR)、出力容量での電圧降下、デューティ・サイクル、スイッチング周波数などの複数の要素の組み合わせによって生じます。

ピーク・ツー・ピーク出力電圧リップルはレール電圧の公差全体に影響するため、数多くのプロセッサ、FPGA(Field-Programmable Gate Array)、ASIC(Application-Specific Integrated Circuit)、SoC(System-on-Chip)のデータ・シートおよびデザイン・ガイドにおいて目標仕様とされています。

リップルをどのように測定したかによって、設計要件を満足できるかどうかが決まることもあります。

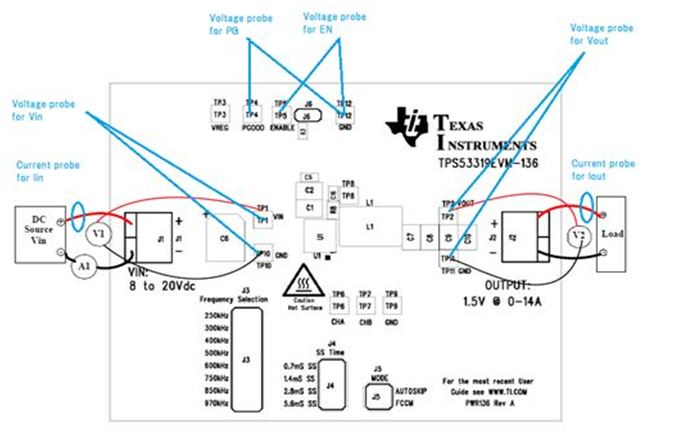

図1には、標準的な出力電圧リップル測定のプローブ接続を示します。

図1: 出力電圧リップル測定のプローブ接続

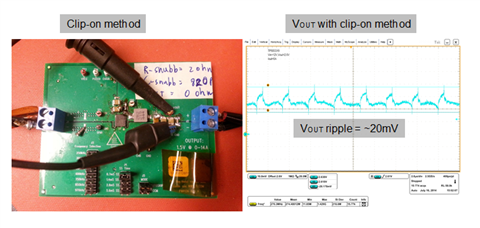

図2に示す、クリップ式プローブを使用したプローブ測定では、グランド線ループでノイズを拾うことに因ると考えられるリップルの増加が見られます。

図2: クリップ式プローブと完全に伸ばした状態のグランド線を使用した出力電圧リップルのプローブ測定。付近のスイッチ・ノードからノイズを拾っている

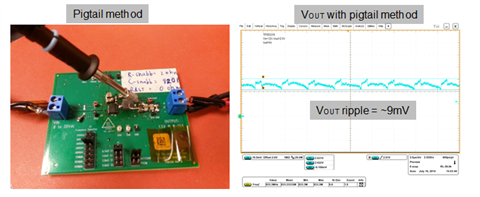

図3に示す、ピグテール方式を使用したプローブ測定では、同様にプローブの先端はスイッチ・ノード付近にありますが、リップルが改善しています。グランド・ループが短縮されているため、ノイズの混入がそれほど深刻ではなくなっています。

図3: ピグテール方式を使用した出力電圧リップルのプローブ測定。プローブのグランドに接続されたピグテールを、基板のグランドに接触させている

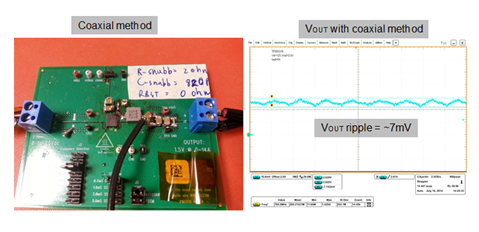

図4に示す、同軸ケーブル方式を使用した測定では、測定結果がさらに改善しています。シールドの編組銅線を基板のグランドに直接ハンダ付けすることで、グランド・ループがさらに最小化されています。

図4: 同軸方式を使用した出力電圧リップルのプローブ測定

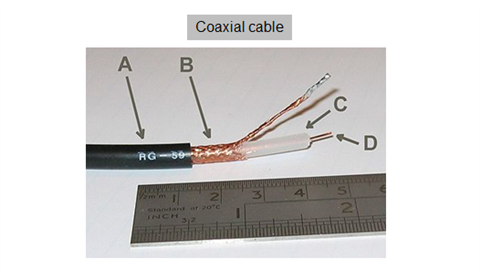

図5に、同軸ケーブルの詳細画像を示します。

図5: 同軸ケーブルの詳細画像:外側プラスチック被覆(a)、編組銅線シールド(グランド)(b)、内部誘電絶縁体(c)、銅芯線(VOUT)(d)

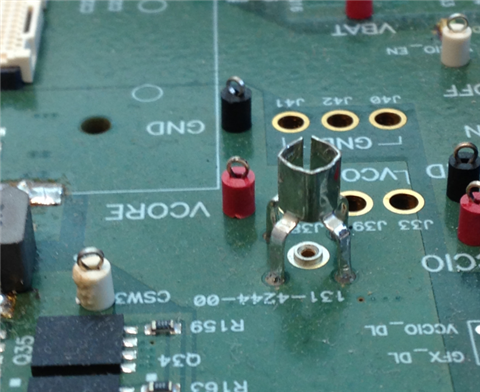

他に同じような測定方法として、図6に示すようなプローブ・ジャックを使用した方法があります。外側のカバーは基板に直接接続されているグランドであると同時に、プローブの先端を電圧テスト・ポイントに接続する役目も果たしています。

図6: プローブ・ジャック

これらすべての測定方法の中でも、リップルを正確に測定するために最適な方法は、おそらく差動プローブを使用した方法でしょう。差動プローブは、特に他の電子機器(電子負荷やマルチメータなど)を同じ基板のグランドに接続している場合に、グランド・ループへのノイズ混入による誤差を取り除くことができます。

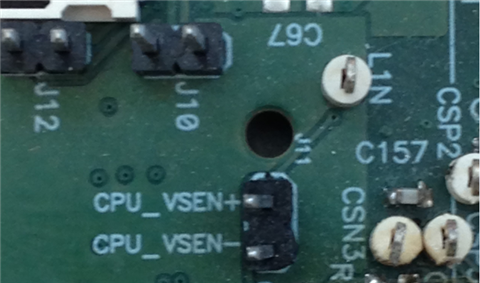

図7に、差動プローブの基板への接続箇所である2つのテスト・ポイントを示します。

図7: 差動プローブのテスト・ポイント、CPU_VSEN+およびCPU_VSEN-

厳しい出力電圧レギュレーション要件を満たす必要があり、ピーク・ツー・ピーク電圧リップルの目標値を低く設定している場合、基板上でのリップルの測定方法が目標達成の鍵となります。プローブ測定の方法を最適化することで、測定結果が改善し、目標仕様を満足できるようになります。この記事で説明した各種のプローブ測定方法を、TPS 40304EVM-353のようなスイッチング・レギュレータ評価モジュール(EVM)等を用いて実際に試し、比較してみてください。また、アプリケーション・レポート『Output Ripple Voltage for Buck Switching Regulator』を読み、WEBENCH Power Designerにおいてリップル電圧がどのような方法で計算され、レポートに表示されるかをよく理解してください。

上記の記事は下記 URL より翻訳転載されました。

*ご質問は E2E 日本語コミュニティにお願い致します。