より小型のパッケージでより処理性能の高いデバイスがますます求められるようになる中、昨今のどの電源でも最も優先度が高いのが電力密度です。絶縁電源トポロジで最も人気が高いのはフライバックですが、従来のフライバックではリーク電流やスイッチング損失のためにスイッチング周波数に限度があり、ソリューションの小型化もしにくくなっています。

高周波数のスイッチングでも、フライバック・トポロジを最適化して効率をはるかに高められる新しい方法があります。この記事では、ゼロ電圧スイッチング(ZVS)が可能なアクティブ・クランプ・フライバック・トポロジで電力密度を高められる仕組みを説明し、さらなる効率向上のためにトポロジを最適化する2通りの方法をご紹介しようと思います。その1つはスイッチ・ノード容量の削減、もう1つは2次共振回路の利用です。

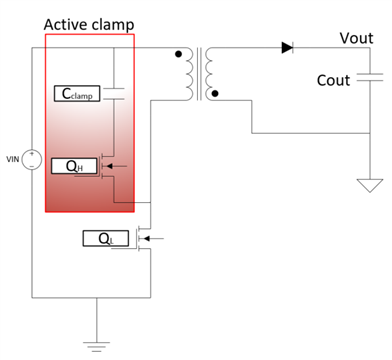

従来のフライバック・トポロジの効率が制限される要因となる部品の1つが、パッシブ・クランプです。これは、スイッチ・ノードと入力電圧の間に配置される抵抗/コンデンサ・ダイオード(RCD)回路を指し、トランスのリーク・インダクタンスを逃がして、1次FET(電界効果トランジスタ)の電圧ストレスを緩和するのが目的です。問題は、リーク電流がすべて無駄なエネルギーとなり、損失を生み出すことです。この方法の変形としてよく使われるのが、図1のアクティブ・クランプ・フライバックです。この場合、パッシブRCDクランプは、アクティブFETとクランプ・コンデンサで置き換えられます。このように構成することで、リーク・エネルギーをコンデンサに蓄積して、スイッチング・サイクルの後の段階で注意深く出力に移すことが可能になるので、効率が向上します。

図1:アクティブ・クランプ・フライバック

アクティブ・クランプを利用するもう1つの利点は、クランプFETを流れる電流を両方向にできることです。これにより、1次FET(図1のQL)のZVSが可能になります。

この方式の重要性を理解するには、まずQLのスイッチング損失を解析する必要があります。スイッチ・ノード(QLのドレイン)の寄生容量を放電したとき、(総スイッチング損失のほとんどを占める)QLのターンオン損失は式1で求められます。

ここで、はターンオン時のスイッチ・ノードの総容量、VSWはターンオン時のスイッチ・ノードの電圧、FSWはスイッチング周波数です。

VSWがゼロに近いとターンオン時のスイッチング損失が事実上無くなるため、スイッチングを高速化してもスイッチング損失を増加させないことが可能になります。アクティブ・クランプ・フライバックが遷移モードの場合は、(図1の)QHを使って、トランスの1次巻線のマイナス磁化電流を蓄積し、その後にその電流を使ってスイッチ・ノード容量を放電することができます。

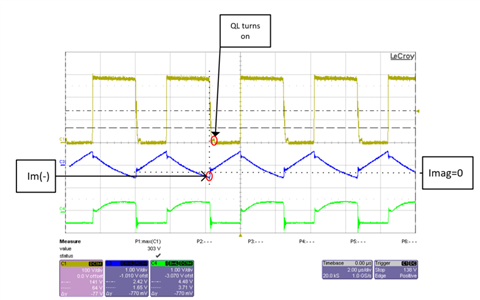

リーク・エネルギーの他に、クランプ・コンデンサは磁化エネルギーの一部も蓄積します。図2に示すように、QHのオン時間を調整することで、マイナス磁化電流(Im-)を流し、ゼロになるまでスイッチ・ノードを放電してからQLをオンにすることができます。

図2:Im-を蓄積してZVSを実現する(黄色:VSW、青:1次電流、緑:2次電流)

Im-は、ZVSを実現するのにちょうどいい量である必要があり、過剰ではいけません。Im-の最低量は、式2で求められます。

マイナス電流が過剰だと、コア損失が大きくなり、動作周波数が低下します。マイナス電流の量を正確に制御するには、TIの『UCC28780』のような専用のコントローラが必要です。

Csw_totalを最小限に抑えることも重要です。スイッチ・ノード容量が増加すると、さらにマイナス電流が必要になるため、コア損失が増加します。式3は、スイッチ・ノードで見られる総容量の主な構成要素を示しています。

ここで、はクランプFET(QH)の総出力容量、は1次FET(QL)の出力容量、はトランスの寄生容量、はブート・ダイオードの寄生容量、は同期整流FETの反射出力容量です。

2つの1次FETが要素として最も重要になる傾向があるため、この部品を選択するときには慎重に検討する必要があります。ZVSを用いると、1次FET(QL)の損失のほとんどは導通損失となります。ここでRDS(on)が仕様として重要になりますが、RDS(on)が減少するときは、それと引き換えにCossが増加することを忘れないでください。それにより、スイッチ・ノード容量が増加します。非常に低いオン抵抗を選んでも、最適な設計にはなりません。50W~100Wのアクティブ・クランプ・フライバック設計では、まずRDS(on)の範囲が150~350mΩのQLを選ぶところから始めるといいでしょう。

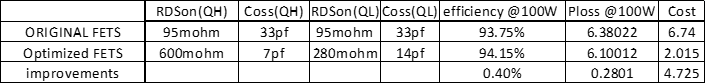

設計で犯しがちな間違いが、QLとQHの両方に同じFETを選んでしまうことです。QHの2乗平均平方根(RMS)電流はQLよりも低く、そのため比較的高いオン抵抗を許容できます。図3では、最適化されたFETと、非常にオン抵抗の低い同じFETを比較したものです。この図から分かるように、効率向上と電力損失削減を、かなりの低コストで達成できます。さらに高い効率が必要な場合は、シリコンFETの代わりに窒化ガリウムFETを使用することでCossをさらに削減できる可能性がありますが、コストは上昇します。

図3:最適化されたFETでは、1/3のコストで効率向上と電力損失削減の効果がある

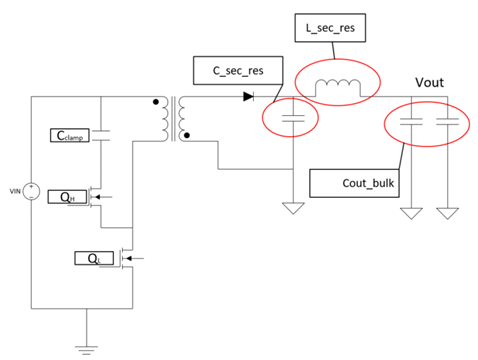

2次共振と呼ば��る手法によりQHのRMS電流を削減することで、さらなる効率向上が可能です。1次共振では、トランスの消磁時間の間、そのリーク・インダクタンスはクランプ・コンデンサのみと共振します。図4に示すように、2次共振では出力に単純なインダクタ/コンデンサ・フィルタを使用して、追加された2次共振コンデンサ(C_sec_res)とリーク・インダクタンスを共振させ、CClamp >> Csec_res/(1次/2次巻線比)2 となるようにします。

図4:2次共振が追加された回路

図5は、同じ回路で1次共振(左図)と2次共振(右図)の両方を用いたものです。両方ともまったく同じ仕様でありながら、2次共振が電流の形を変化させ、1次RMS電流を減少させたことがはっきりと分かります。2次共振を使用することで、トランスの1次巻線とQHの両方で導通損失が減少します。入力電圧がより低いときに効率向上が大きく、このとき1次電流は最大です。多くの場合、2次共振を実装すると、90VACで1%の効率向上が得られます。

図5:2次共振により1次側の電流が減少する(黄色:VSW、青:1次電流、緑:2次電流)

適切に設計した場合、アクティブ・クランプ・フライバックを用いることで、驚くほどの効率と電力密度を実現できます。重要なのは、最適なマイナス電流で遷移モード動作を維持するコントローラを使用することです。

次にアクティブ・クランプ・フライバックを設計するときには、最適なFETを選択してスイッチ・ノード容量を最小限に抑えることと、効率と熱特性の向上のために2次共振回路を追加することの重要性を思い出してください。

著者紹介

Sarmad Abedin(Texas Instruments)