GaN (窒化ガリウム) はパワー・エレクトロニクス分野で一般的なトピックになっています。GaN を採用すると、80 Plus Titanium 対応の電源や、3.8kW/L の電気自動車 (EV) 向けオンボード・チャージャ、EV 充電ステーションなどを実現できるからです。電力密度と効率を向上させる能力がある GaN は、多くのアプリケーションで従来の MOSFET (金属酸化膜半導体電界効果トランジスタ) に代わって使用されています。ただし、GaN を使用した設計では、その電気的特性や実現可能な性能に関して、シリコンとは異なる一連の課題に直面することになります。

GaN FET には、デバイスの構造に関して複数の種類が存在します。デプリーション・モード (D モード)、エンハンスメント・モード (E モード)、およびカソードへのカスケード接続(カスコード)です。それぞれに独自のゲート・ドライバ要件とシステム要件があります。この記事では、システム設計で電力密度を高めるために各種の GaN FET を使用して設計を行う際の最も重要な検討事項について詳しく説明します。また、ゲート・ドライバや電源電圧レギュレーションのような機能の統合によって設計全体を大幅に簡素化する方法についても解説します。

GaN FET の構造

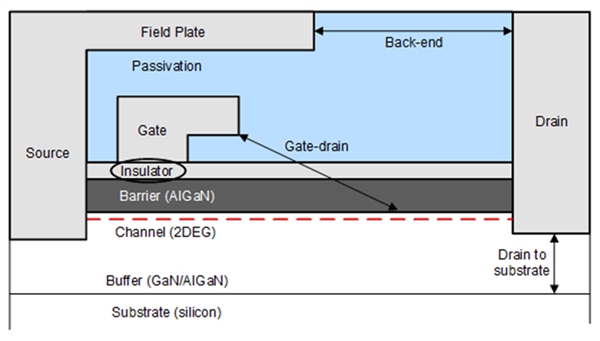

各 GaN パワー・スイッチは、適切なゲート・ドライバと組み合わせる必要があります (そうしないと、卓上でテストを行うときに破裂や発煙が生じる可能性があります)。従来の MOSFET とは異なり、GaN デバイスは HRMT (高電子移動度トランジスタ) であるため、感度の高い独自のゲートを形成できます。図 1 に示す HEMT の断面図は MOSFET に似ていますが、電流はサブストレートやバッファ層全体を経由するのではなく、2 次元の電子ガス層を経由して流れます。

図 1:GaN FET の水平構造断面図

図 1:GaN FET の水平構造断面図

GaN FET のゲート制御が不適切であると、絶縁層、バリア、または他の構造要素のブレークダウンが発生します。デバイスは、そのようなシステム条件の発生中に不具合を引き起こすだけでなく、永続的な損傷を受ける可能性も高くなります。このように敏感な特性を持つため、さまざまな種類の GaN デバイスとそれぞれの幅広い要件について事前に確認する必要があります。また、HEMT は従来のドープ型 FET 構造を採用していません。ドープ型は P-N 接合を形成し、この接合はボディ・ダイオードとして機能します。言い換えると、HEMT には内部ダイオードがないので、このようなダイオードがブレークダウンすることも、逆回復期間中に望ましくない動作を引き起こすこともありません。

ゲート・ドライバとバイアス電圧の検討事項

E モード GaN FET は、多くの技術者が既に使用した経験のある E モードのシリコン FET に非常によく似ています。1.5V ~ 1.8V の正電圧で FET のターンオンが始まります。これは、ゲート・スレッショルドを 6V と規定している大半の動作条件の場合に該当します。ただし、ほとんどの E モード GaN デバイスは最大ゲート・スレッショルドを 7V と規定しており、この規定に反した場合、永続的な損傷が生じる可能性が高くなります。

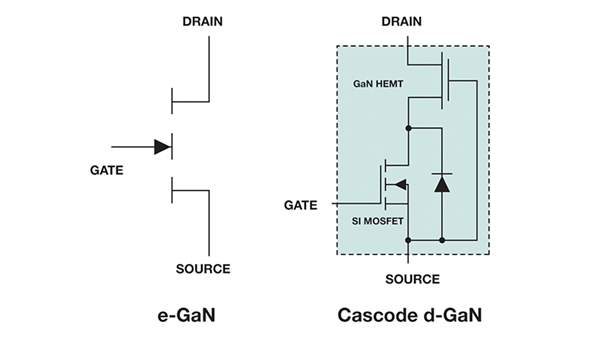

従来のシリコン・ゲート・ドライバでは、適切な電圧レギュレーションが得られない場合や GaN ベースの設計で高い同相過渡耐性を実現できない場合があるので、多くの設計者は 『LMG1210-Q1』のようなゲート・ドライバを選択します。この製品は、GaN FET との組み合わせを想定して TI が専用設計したものです。このデバイスは、電源電圧にかかわらず、5V のゲート・ドライブ電圧を供給します。従来のゲート・ドライバを使用する場合には、GaN FET に過剰なストレスを生じさせないように、ゲート・ドライバに供給するバイアス電圧の非常に厳格なレギュレーションが必要です。図 2 に示すカスコード GaN FET は、E モード GaN FET に比べて使いやすさを優先した妥協案です。

図 2:E モードとカスコード D モードの GaN FET を表すシンボル

図 2:E モードとカスコード D モードの GaN FET を表すシンボル

この GaN FET は D モード・デバイスです。つまりノーマリー・オンであり、デバイスをオフにしておくには、負のゲート・スレッショルドを用意する必要があります。パワー・スイッチとしては、この仕様は大きな問題を招きます。そのため、メーカー各社は 30V のシリコン FET を GaN FET に対して直列の位置に追加し、これらを 1 つのパッケージとして販売しています。この場合、GaN FET のゲート端子をシリコン FET のソース端子に接続し、ターンオンとターンオフそれぞれのゲート・パルスをシリコン FET のゲート端子に印加します。

このアプローチの最大の長所は、『UCC5350-Q1』のような従来型の絶縁型ゲート・ドライバを使用してシリコン FET を駆動でき、ゲート・ドライバとバイアス電圧に関する多くの懸念を排除できることです。一方、カスコード GaN FET の大きな短所は、FET 全体の出力静電容量が大きくなること、およびボディ・ダイオードが存在するので逆回復の影響を受けやすくなることです。GaN FET の出力静電容量にシリコン FET の出力静電容量とが加算されるため、GaN FET 単体に比べて静電容量が 20% 増加します。つまり、GaN を使用する他のソリューションに比べて、スイッチング損失が 20% 以上大きくなります。逆導通の期間中、シリコン FET のボディ・ダイオードは導通して電流を流し、電圧極性が反転した時点で逆回復が発生します。

カスコード GaN FET は、シリコン FET のアバランシェ・ブレークダウンを防止するために 70V/ns のスルーレート (他の GaN ソリューションでは 150V/ns) で動作するので、スイッチング・オーバーラップ損失が大きくなります。他のソリューションに比べて、カスコード GaN FET を使用する設計の方がシンプルですが、実現可能な性能が制限されます。

統合によってソリューションを簡素化

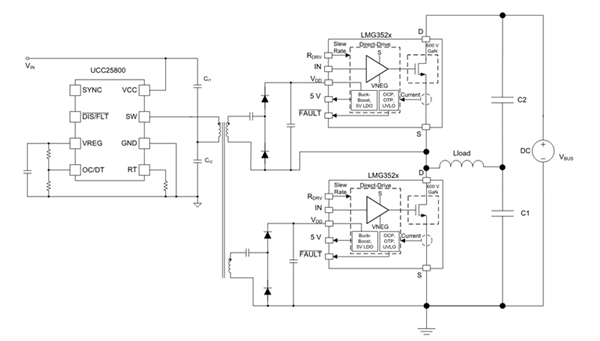

バイアス電圧レギュレーション機能を備えたゲート・ドライバと、D モード GaN FET を統合することにより、E モード GaN FET やカスコード GaN FET での設計に伴う多くの課題を解決できます。使用している GaN FET は D モードなので、この GaN FET に対して直列の位置にシリコン FET を内蔵しています。ただし、カスコード GaN FET と比較した場合の大きな違いは、内蔵のゲート・ドライバが GaN FET のゲートを直接駆動できることです。シリコン FET は、パワー・オンの際にノーマリー・オフのイネーブル・スイッチという役割を果たします。このアプローチを直接駆動 (ダイレクト・ドライブ) といいます。長所は、カスコード GaN FET で大きな課題であった出力静電容量の増加、逆回復による影響、直列接続したシリコン FET のアバランシェ・ブレークダウンをいずれも排除できることです。『LMG3522R030-Q1』の内蔵ゲート・ドライバは、スイッチング・オーバーラップ損失を非常に小さくできるので、GaN FET を最大 2.2MHz のスイッチング周波数で動作させることができます。また、GaN FET を不適切なゲート・ドライバと組み合わせてしまうリスクを排除できます。図 3 に、統合型 GaN FET である『LMG3522R030-Q1』を使用したハーフブリッジ構成の例を示します。

図 3:トランス・ドライバ『UCC25800-Q1』と 2 個の『LMG3522R030-Q1』GaN FET を使用した簡素化 GaN ハーフブリッジ構成

図 3:トランス・ドライバ『UCC25800-Q1』と 2 個の『LMG3522R030-Q1』GaN FET を使用した簡素化 GaN ハーフブリッジ構成

内蔵ドライバはソリューション・サイズの小型化に貢献し、電力密度の高いシステムを実現しやすくなります。また、昇降圧コンバータを内蔵することで、9V ~ 18V の非レギュレーション電源と組み合わせて 『LMG3522R030-Q1』を動作させることができます。その結果、バイアス電圧の要件を大幅に軽減できます。小型でより低コストのシステム・ソリューションを製作するために、『LMG3522R030-Q1』を、『UCC25800-Q1』など EMI (電磁干渉) が非常に小さいトランス・ドライバと組み合わせることができます。このドライバは、2 次側の複数の巻線を使用して開ループの LLC (インダクタ-インダクタ-コンデンサ) 制御を実行します。または、『UCC14240-Q1』DC/DC モジュールのような高集積の小型バイアス電源を使用し、デバイスに電力をローカル供給することもできます。それにより、PCB (プリント基板) の占有面積が小さい低背の設計を実現できます。

まとめ

GaN デバイスを適切なゲート・ドライバやバイアス電圧と組み合わせることで、システム・レベルでさまざまなメリットが得られます。たとえば、150V/ns のスイッチング速度、スイッチング損失の低減、産業用や車載用の大電力システム内の磁気素子の小型化などです。統合型の GaN ソリューションを採用すると、デバイス・レベルのさまざまな課題を簡素化できるため、設計者はより多様なシステムに注目できます。

参考情報:

+ホワイト・ペーパー:

”ドライバの統合によるGaN性能の最適化”

”電力密度を高めるためのトレードオフとテクノロジに関する理解”

”Direct Drive Configuration for GaN Devices(英語)”

+リファレンス・デザイン:

”180W/in³ (10.98W/立方 cm) を上回る電力密度を達成する、3.6kW の単相トーテム・ポール・ブリッジレス PFC”

”6.6kW、3 相、3 レベル ANPC インバータ / PFC 双方向電力段”

※すべての登録商標および商標はそれぞれの所有者に帰属します。

※上記の記事はこちらの技術記事(2022年3月14日)より翻訳転載されました。

※ご質問はE2E Support Forumにお願い致します。