近年は、トラクション インバータの設計でシリコン カーバイド(SiC )電界効果トランジスタ(FET ) の採用例が大幅に増加してきました。その主な理由は、SiC FET が高いスイッチング周波数で動作し、電力密度を向上させると同時に、高い効率を維持することができるからです。一方、SiC インバータは 100V/ns を上回る大きな過渡電圧 (dv/dt) 信号を生成する可能性があるため、同相過渡電圧耐性 (CMTI) に関する懸念が生じます。これは、インバータのゲート ドライバ向け絶縁型バイアス電源を設計する際の新たな課題となります。

絶縁型バイアス電源にはいくつかのトポロジがありますが、コスト性能比が最も優れているのは 1 次側安定化 (PSR) フライバック コンバータです。このトポロジには、少ない外部部品点数、厳密な出力電圧安定化、フォトカプラ不要、高効率、信頼性の高いガルバニック絶縁という特長があります。SiC インバータ内での PSR フライバックの耐性向上に役立つ、CMTI の効果的な改善方法を利用すれば、SiC FET と絶縁型バイアス電源の組み合わせで PSR フライバックを引き続き使用することができます。

PSR フライバックを絶縁型バイアス電源として使用

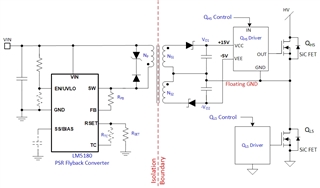

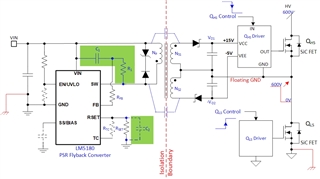

図 1 に、TI の LM5180 コンバータを使用する、トラクション インバータ アプリケーション内の PSR フライバック コンバータ トポロジを示します。LM5181、LM25180、LM25183、LM25184 の各コンバータや LM5185 コントローラなどの PSR フライバック デバイスはいずれも、LM5180 と共通のアーキテクチャを備えています。これらの製品の間の主な違いは、取り扱える電力の大きさです。

図 1 には、インバータ SiC FET の 1 個のハイサイド ドライバにバイアス電圧を供給する 2 本の出力レールのみを示しています。より多くの巻線をトランスに結合する方法で、絶縁型出力をさらに追加することも可能です。破線で示した部品は、追加の機能に対応するオプション部品です。

図 1:トラクション インバータ向けの PSR フライバック バイアス電源

従来型のフライバック コンバータは通常、厳格な出力安定化を目的としてフィードバック回路を形成するために、2 次側に 1 個のフォトカプラと、TI の TLV431 のような電圧リファレンスを必要とします。それに対し、PSR フライバック コンバータはトランスの 1 次側巻線を通じて出力電圧をセンスし、絶縁型電圧レールの厳格な出力電圧安定化を行うので、フォトカプラや 2 次側フィードバック回路は必要ありません。その結果、コスト性能比の優れたシンプルなバイアス電源ソリューションを製作できます。

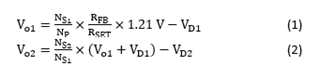

具体的には、次の式 1 と式 2 で出力電圧が決まります。ここでは、Vo1 がメイン出力 (より大きい電力) であると仮定します。

ここで、1.21V はコンバータ IC のリファレンス電圧です。NP、NS1、NS2 はそれぞれ、対応するトランス巻線の巻数です。RFB と RSET はそれぞれ、出力電圧センシング抵抗と安定化設定抵抗です。VD1 と VD2 はそれぞれ、2 個の出力ダイオードの順方向電圧降下です。

RSET は通常、LM5180、LM5181、LM5183、LM5184 の場合は 12.1kΩ、LM5185 の場合は 10kΩ に固定されます。したがって、式 1 を次のように書き直すことができます。

式 3 は、RFB を流れる 100μA の動作電流がノイズの影響を受けなければ、出力電圧が安定した状態にとどまることを示しています。

CMTI の課題

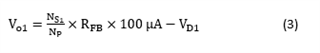

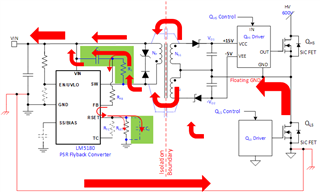

図 2 に示すように、SiC FET が数ナノ秒 (ns) 単位でスイッチング動作する場合、SiC FET ドライバのフローティング グランドでもあるインバータ レッグのスイッチ ノードは 100V/ns を上回るスルーレートで変化します。

図 2:標準的な PSR フライバック バイアス電源で生じる CMTI

フローティング グランドで生じる大きな dv/dt は、絶縁型バイアス電源にとって同相過渡(CMT ) となります。図 2 はまた、この CMT が、トランスの寄生コンデンサ (破線で表現) を経由して 1 次側へ流れる CMT 電流を誘導することも示しています。この CMT 電流の一部は RFB を経由して流れ、安定動作に影響を及ぼします。

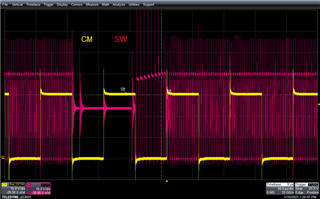

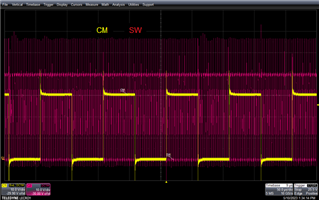

図 3 に、CMTI の影響を受けた通常の PSR フライバックの代表的な波形を示します。これは、標準の LM5180EVM-S05 評価基板 (EVM) を使用してキャプチャしたものです。黄色の波形は SiC レッグの CMT です。赤色の波形は、PSR フライバックの SW ピンの電圧です。

この間欠的なスイッチング動作について説明します。PSR フライバックの出力サンプル アンド ホールド期間内での CMT は、フィードバック信号に影響を及ぼします。これは CMT 電流が、式 3 に示した 100μA の動作電流に影響するからです。影響を受けたフィードバック信号は、安定動作から誤って逸脱する方向へとコンバータを導きます。その結果、スイッチングが間欠的になり、出力への安定的な電力伝達に中断が生じます。出力電圧は降下する可能性があり、その場合は SiC インバータの動作に影響を及ぼすことになります。

図 3:CMT の影響を受けた PSR フライバック (縦軸:チャネル 1 = 100V刻み、チャネル 2 = 10V刻み。横軸:50μs刻み)

PSR フライバックにおける CMTI の改善

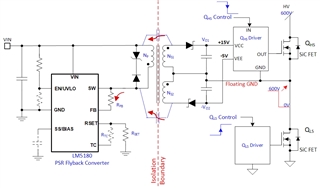

図 4 に、提案する CMTI 改善方法を示します。この方法では、RFB に対して直列に 1 個の抵抗 (R1) を追加し、2 個のフィードバック抵抗の接合部と VIN ピンの間に 1 個のセラミック コンデンサ (C1) を追加します。この抵抗とコンデンサはローパス フィルタを形成し、RFB に流れる 100μA の動作電流に対する CMT 電流の影響を軽減します。オプションとして第 2 のフィルタ コンデンサ (RSET ピンに接続する C2) を使用すると、軽減効果をさらに高めることができます。

図 4:PSR フライバックにおける CMTI の改善

図 5 に、CMTI 改善方法の動作原理を示します。矢印のサイズの違いは、さまざまなパスに流れる CMT 電流の相対的な大きさを表します。フィードバック信号に対する CMT 電流の影響が大幅に小さくなっていることがわかります。

図 5:PSR フライバックにおける CMTI の改善により、CMT 電流がフィードバック信号に及ぼす影響が減少

概念実証

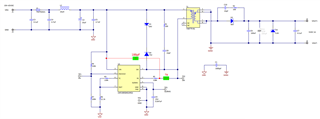

LM5180EVM-S05 や LM5185EVM-SIO を含め、TI のいくつかの PSR フライバック コンバータ ボードを使用して、提案した CMTI 改善方法を検証すると、予期した改善が実証されました。図 6 に、この方法を実装した LM5180EVM-S05 の回路図を示します。

図 6:CMTI 改善のために LM5180EVM-S05 に加えた変更

図 7 に、この CMTI 改善方法を実装した評価基板 (EVM) の性能を示します。図 3 と同じ動作条件の下で、コンバータの動作は大幅に改善されており、明確な中断は見られません。LM5185EVM-SIO でも同様の改善を確認しました。

図 7:CMTI 改善方法を実装した LM5180EVM-S05 の性能 (縦軸:チャネル 1 = 100V刻み、チャネル 2 = 10V刻み。横軸:50μs刻み)

まとめ

提案した CMTI 改善方法を実装することで、PSR フライバックは引き続き、絶縁型バイアス電源として魅力的かつ適切なソリューションです。SiC インバータに限らず、SiC FET を採用するオンボード チャージャ、バッテリ管理システム、大電力 DC/DC コンバータなどにも利用できます。