隨著衛星和太空探索的發展,業界持續提高內建運算能力以進行即時處理。因此,對於負載點電源系統的需求也在不斷演進,需要更高水準的功率、性能和更高的效率,同時也面臨更小的電路板空間和高可靠性需求的挑戰。

輻射強化低壓降穩壓器(LDO)仍然是許多航太級子系統的重要電源元件,包括現場可程式化設計邏輯閘陣列(FPGA)、資料轉換器和類比電路。對於性能取決於乾淨輸入的元件,LDO 有助於確保為其提供穩定、低雜訊和低漣波的電源供應。

但市面上有如此多的 LDO,您如何為您的子系統選擇合適的輻射強化裝置?

大幅減少雜訊

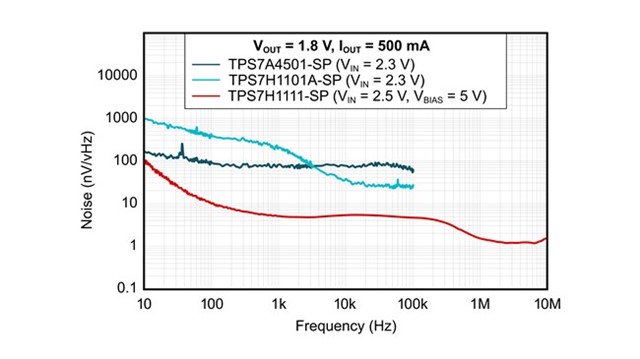

為了為高效能時脈、資料轉換器、數位訊號處理器或類比元件提供乾淨、低雜訊的電源軌,必須將 LDO 電路產生的內部雜訊最小化。由於不容易濾除內部產生的 1/f 雜訊,因此應尋找固有低雜訊特性的 LDO。低頻雜訊通常是最大且最難濾除的雜訊。TPS7H1111-SP 提供最低 1/f 雜訊位準之一,在 10 Hz 時峰值約為 100 nV/√Hz。圖 1 顯示雜訊頻譜密度隨頻率的變化。

圖 1:TI 航太級 LDO 雜訊比較

PSRR

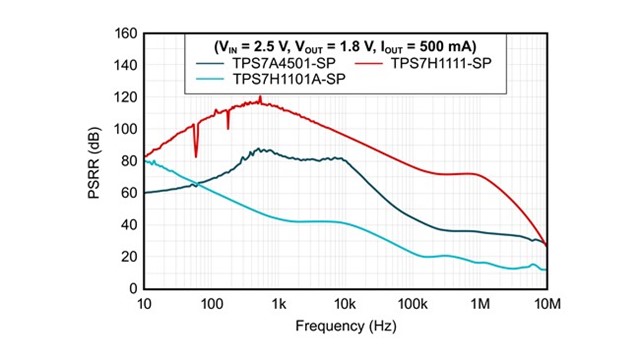

電源供應拒斥比(PSRR)衡量 LDO 清除或抑制來自其他上游元件(例如開關電源)的傳入雜訊能力。對於高階類比數位轉換器(ADC)而言,輸入電源雜訊要求越來越嚴格,以盡量減少位元錯誤。在較高頻率下很難獲得高 PSRR,因為它需要來自控制環路的快速響應。通常,設計人員需要使用外部元件來過濾雜訊以達到有效的 PSRR,這會增加解決方案的尺寸。對於航太應用來說,這是再明顯不過的問題,因為尺寸和重量都與衛星發射成本直接相關。

此外,由於切換諧波,PSRR 高於此頻率非常重要。如果您正在尋找良好的 PSRR,TPS7H1111-SP LDO 提供顯著的性能優勢,尤其是在較高頻率範圍內,在 1 MHz 時 PSRR 為 70 dB(請參閱圖 2)。

圖 2:TI 輻射強化 LDO PSRR 比較

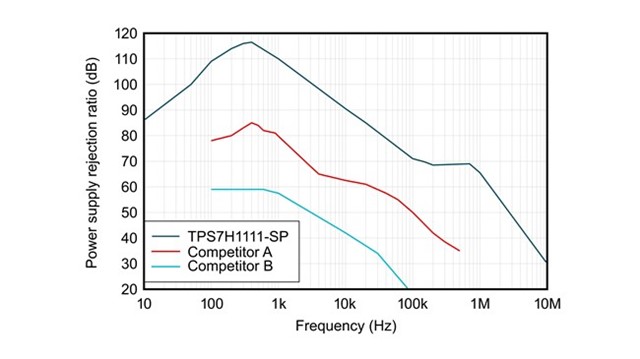

與其他輻射強化 LDO 相比,TPS7H1111-SP 在較低頻率下提供類似或更好的 PSRR 性能,並在較高頻率下提供顯著改進。隨著設計人員不斷提高上游切換穩壓器的切換頻率,這一點尤其重要(請參閱圖 3)。

圖 3:業界標準的輻射強化 LDO PSRR 性能

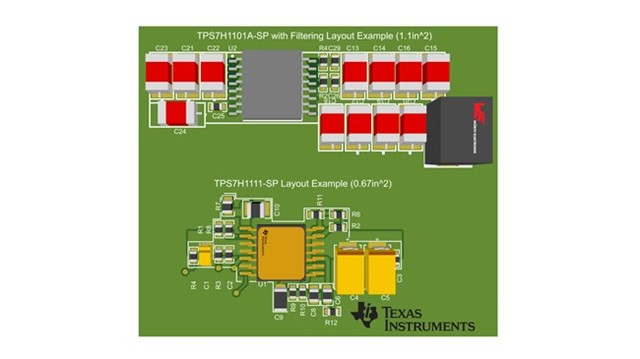

TPS7H1111-SP 改進的 PSRR 性能無需離散式濾波器,有助於縮小整體解決方案的尺寸和重量。

圖 4 顯示一個範例配置,其中包含 TPS7H1101A-SP 以及實現可接受的 PSRR 等級所需的其他離散式元件。TPS7H1111-SP 的性能提升可提供更好的 PSRR,並將解決方案尺寸縮小約 40%。

圖 4:使用 TPS7H1111-SP 縮小濾波器尺寸

其他重要的 LDO 特色

除了 PSRR 和雜訊之外,還有其他影響衛星性能和效率的設計考量。

電力在太空中是一種有限的資源,因為太陽能面板只能提供定量的電力。啟用功能可讓您指定 LDO 在任何給定時間是否應開啟或關閉,有助於整體節省功率預算。觸發針腳對於開機順序也很重要,這在新一代 FPGA 中越發重要。

在接近最小壓降電壓的情況下運作可以進一步提高電源效率。LDO 的壓降電壓是輸入和輸出電壓之間的電壓差,此時 LDO 停止調節輸出電壓。壓降電壓規格越小,操作電壓差越低,進而降低功耗和散熱功能,並從本質上提高最大效率。TPS7A4501-SP、TPS7H1101A-SP 和 TPS7H1111-SP 皆支援相當小的壓降電壓。然而,為了不限制 PSRR 性能,考慮負載條件、輸出電容和空餘空間至關重要。

電力並不是唯一的設計挑戰。較新的航太級 FPGA(例如 Xilinx KU060 或 Versal XQR VC1902)對每個電源軌都有嚴格的輸入電壓容差要求,以便將其性能最佳化。為了滿足嚴格的準確度要求,您必須考慮輻射暴露和壽命終止條件下的準確度。TPS7H1111-SP 在線路、負載、溫度和輻射方面具有 ±1.5% 的準確度。

提供可靠的電源軌(尤其是在啟動時)將有助於防止下游元件損壞。軟啟動功能可防止電壓上升過快,否則可能導致電流過衝或峰值突入電流過大。軟啟動還可以防止上游電源上的過電流消耗,進而防止不可接受的電壓下降程度。

雖然 TPS7H1111-SP 透過消除對離散式濾波器的需求來協助提高功率密度,但還有其他方法可以減小解決方案尺寸,包括限制 LDO 的外部元件數量及其實際佔位面積。TI 的 TPS7A4501-SP 是業界封裝尺寸、配置和解決方案尺寸最小的輻射強化 LDO 之一。另外,我們用於低地球軌道任務的太空強化塑膠(-SEP)新版本更可將佔位面積尺寸減少 30% 至 50%,有助於提高功率密度。TPS73801-SEP 和 TPS7H1111-SEP 是這些塑膠耐輻射解決方案如何不斷改進尺寸、重量和功率的最新範例。

結論

在太空中為對雜訊極為敏感的軌道供電是一項動態挑戰,需要在效率、可靠性、性能、尺寸和重量之間進行取捨。並非所有應用都需要高性能 LDO。如果您正在設計低性能類比電路或使用容差要求不那麼嚴格的舊版 FPGA,您還是可以擁有小尺寸、低成本的解決方案,同時保留可接受的功能等級。

其他資源

- 閱讀 TI E2E

設計支援論壇常見問題集「負載條件、輸出電容和空餘空間如何影響我的航太級 LDO 電源供應拒斥比 (PSRR) 性能?」

- 下載 TI 航太產品指南和電子產品的輻射手冊。