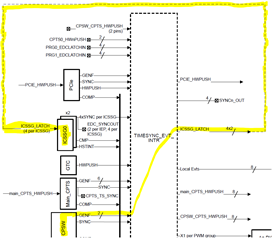

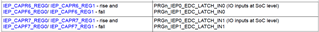

I am using a Sitara processor with a Linux core, a time sync router, and a PRU subsystem (AM62x, AM64x, AM65x). I want to synchronize the Linux system time with an IEP timer in the PRU subsystem. How do I do it?

We will use AM64x for this example, but the same concepts will apply to all of the processors.

.

AM64x Time Sync Router: reference [FAQ] AM64x: What is the Time Sync Router for? How do I use it?

AM62x Time Sync Router: reference [FAQ] AM62: What is the Time Sync Router for? How do I use it?

For more information about other Sitara multicore subjects, reference [FAQ] Sitara multicore development and documentation. More information about PRU specifically can be found in the PRU Development subsection.