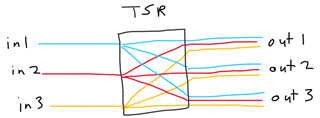

AM64x has interrupt routers, just like any other processor. But it also has an interrupt router called the Time Sync Router (TSR) that is designed to route an input interrupt to multiple output interrupts. What is the TSR for? The documentation is not very clear at the moment, so how do I use it?

.

For information about Time Sync Router on AM62x, reference this FAQ: e2e.ti.com/.../faq-am62-what-is-the-time-sync-router-for-how-do-i-use-it