前稿では、各データ・ビットを分解し、伝送するシンプルなシリアル・インターフェイスについて解説しました。また、このタイプのインターフェイスの使用は通常、低分解能または低速のADCに限定されることも述べました。

最新の高分解能(12ビット超)の逐次比較型(SAR)アナログ/デジタル・コンバータ(ADC)は、ほとんどの場合、冗長/エラー補正技術の採用により、特に高スループット・レートでのADCの性能を向上しています。こうしたADCでは、最終的な変換結果は、すべての変換処理の完了後にのみ得られます。

インターフェイス・タイプ2:変換処理が完了次第、データ・ビットを伝送

このタイプのADCは、サンプルSの変換処理が完了すると変換結果をホスト・コントローラに伝送し、その間に次のサンプルS+1を取りこみます。ホスト・コントローラは、サンプルSの変換結果を受けとってから初めて、サンプルS+1に対する変換開始(SOC)信号を発します。

ADCとホスト・コントローラ間のデータ伝送は、パラレル方式かシリアル方式が可能です。

図1にパラレル・インターフェイスの例を示します。

パラレル・データ伝送には次の式が成り立ちます。

- tDTX = tCLK

- tRESP-ADC = tCONV + tCLK

- tTHROUGHPUT = tCONV + tACQ

- tRESP-ADC ≤ tTHROUGHPUT

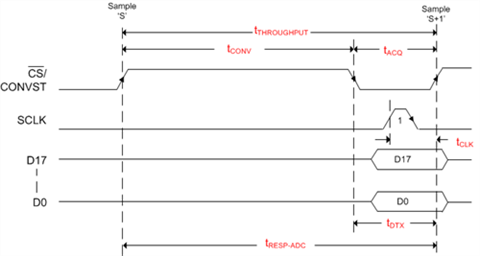

図2はADS 8881に実装される簡易型シリアル・インターフェイスを示します。

図2:ADS 8881で使用される簡易型のタイプ2のシリアル・インターフェイス

図2:ADS 8881で使用される簡易型のタイプ2のシリアル・インターフェイス

シリアル・データ伝送には次の式が成り立ちます。

- tDTX = n*tCLK

- tRESP-ADC = tCONV +n* tCLK

- tTHROUGHPUT = tCONV + tACQ (n*tCLK < tACQ、つまり高速クロックの場合)

- tTHROUGHPUT = tCONV + n* tCLK (n*tCLK > tACQ、つまり低速クロックの場合)

- tRESP-ADC ≤ tTHROUGHPUT

ADS 8881を使用する一般的な制御システムでは、ホスト・コントローラは次のような動作をします。

- 変換開始信号を発し、変換完了を待機

- データ伝送フレームを開始し、サンプルSの変換出力データを受信

- 受信データに基づき制御動作を実行

- 次の変換開始信号を発して制御動作の効果を確認

式から明らかなように、タイプ2のインターフェイスを採用するSAR ADCはいずれも、所望のスループットを実現するには最小クロック速度の制約が伴います。

- tCLK < (tTHROUGHPUT - tCONV)/n

ADS 8881を例にとると、

- tTHROUHGPUT = 1µs、tCONV = 710 ns、n = 18

- 1Mspsのスループットを達成するにはtCLK < (1,000 – 710)/18(すなわち、fCLK > 62 MHz)

となります。

クロック速度が遅くなると、応答時間とスループットが遅くなります。

- fCLKが62MHzの場合、tRESP-ADC = tTHROUGHPUT = 1µs

- fCLKが26MHzの場合、tRESP-ADC = tTHROUGHPUT = 1.4µs

- fCLKが16MHzの場合、tRESP-ADC = tTHROUGHPUT = 1.4µs

このシリーズの次稿では、クロック速度が低下してもSAR ADCの高スループットの維持を可能にする別のタイプのシリアル・インターフェイスについて解説します。低下するのはどのパラメータだと思いますか?

その他のリソース:

- さまざまな産業用データ・アクイジション・アプリケーションに最適な、SAR ADCを使用した5つの TI Designsリファレンス・デザイン

- SAR ADC向けSPICEシミュレーション・ツールにより、高精度で容易なコンピュータベースの性能評価が可能になります。詳細はTIのHarsha Munikotiが執筆したブログ(英語)をご覧ください。

- SAR ADC Response Timesシリーズの他のブログ(英語)

- TIの高精度アナログ・エキスパートが設計のヒントとコツをTI E2E CommunityのPrecision Data Convertersフォーラムで解説しています。

上記の記事は下記 URL より翻訳転載されました。

*ご質問は E2E 日本語コミュニティにお願い致します。