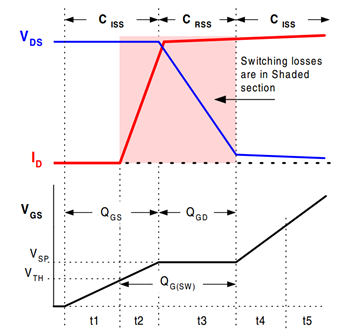

「DC/DCコンバータのデータシート」シリーズへようこそ。前回はシステム効率について取り上げましたが、今回はDC/DCレギュレータ部品のスイッチング損失について、まずは第1部の図3(ここでは図1)に示した、時間に対するVDSおよびIDの曲線から説明します。

図1: スイッチング損失

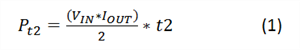

まずは内蔵ハイサイドMOSFETでのスイッチング損失について見てみましょう。各スイッチング・サイクルの開始時に、ドライバは内蔵MOSFETのゲートへの電力供給を開始します。第1部の内容から、MOSFETには端子間に寄生容量があることがわかっています。最初の期間(図1のt1)中、ゲート-ソース間電圧(VGS)はMOSFETのスレッショルド電圧VTHに近づきますが、ドレイン電流はゼロです。そのため、この期間での電力損失はゼロになります。t2の期間では、MOSFETの寄生入力容量(CISS)が充電を開始し、ドレイン電流がMOSFETに流れ始めて直線的に増加します。降圧トポロジの場合、この電流は負荷電流であり、ドレイン-ソース間電圧(VDS)は入力電圧(VIN)です。そのため、2番目の期間(t2)中には、次の式1で表される電力損失が発生します。

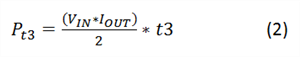

MOSFETの入力寄生容量が充電されると、MOSFETに負荷電流が流れ、VDSが低下し始めます。この期間は、ミラー容量(CGD)の充電だけにかかる時間なので、“ミラー時間”とも呼ばれています。ミラー時間中、ドレイン電流はIOUTに保持され、VDSはVINから低下します。この期間中の電力損失は、次の式2のように表されます。

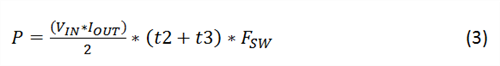

合計スイッチング損失の計算は、次の式3のようになります。

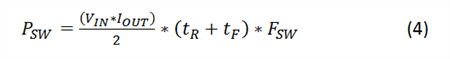

図1では、t2が3番目の期間(t3)より大幅に短くなっています。そのため、式では損失をt3の期間での損失のみとして見積もることができます。このような有限の遷移時間は1つの期間に2回発生します。つまり、MOSFETがオンになったとき(寄生容量の充電時)と、オフになったとき(寄生容量の放電時)の2回です。そのため、両方のケースにおけるt3の期間をMOSFETの立ち上がり時間と立ち下がり時間として見積もることで、次の式4を使ってスイッチング損失を見積もることができます。

スイッチング損失は、周波数と入力電圧に依存します。そのため、入力電圧とスイッチング周波数が高くなると、全体の効率は比較的低くなります。軽負荷時には、LM 2673非同期降圧レギュレータは不連続導通モードに移行します。このモードに移行しても、デバイスはスイッチング周波数を維持します。各サイクルにおいて、集積回路(IC)の内部では電力消費が発生します。そのため、軽負荷時の導通損失は無視できますが、常に存在するスイッチング損失がデバイスの効率に影響します。また、出力に供給される平均電力が極めて低いことから、デバイスの全体的な効率も低くなります。

現在、SIMPLE SWITCHER®ファミリの最新のレギュレータは、負荷が減少するとスイッチング周波数を低下させる、パルス周波数変調(PFM)を備えています。これにより、負荷が非常に軽い場合や無負荷の場合でも、レギュレータで高効率を維持できるようになります。

LM 2673は非同期デバイスなので、MOSFETがオフになると順方向バイアスとなるキャッチ・ダイオードを備えています。遷移時間がゼロでない場合の原理がキャッチ・ダイオードにも同じように適用されます。ただし、ダイオードの電圧スイングはグランドからダイオードの順方向電圧降下(VF)までしかないため、ダイオードでのスイッチング損失は無視できます。また、LM 2673のようなSIMPLE SWITCHERレギュレータのスイッチング周波数は250kHzと比較的低いので、インダクタのコアで発生するスイッチング損失も無視できます。

このシリーズの次の(そして最後の)回では、DC/DCレギュレータ回路のMOSFETとパッシブ部品における導通損失について説明し、合計損失および結果として得られる効率の計算式を紹介します。

その他のリソース

- LM 43603 SIMPLE SWITCHER 3.5V~36V、3A同期降圧型コンバータのデータシートを日本語ダウンロードしてください。

- LM 2673 SIMPLE SWITCHER 3A降圧型電圧レギュレータ(電流制限調整機能付き)を日本語ダウンロードしてください。

- 「DC/DCコンバータのデータシート - システム効率についての解説」をご覧ください。

- 今すぐWEBENCH Power Designerで設計を開始しましょう。

- TIのSIMPLE SWITCHER DC/DCレギュレータの幅広いポートフォリオについて詳細をご確認ください。

上記の記事は下記 URL より翻訳転載されました。

*ご質問は E2E 日本語コミュニティにお願い致します。