Other Parts Discussed in Thread: THS3215, THS3217, OPA838

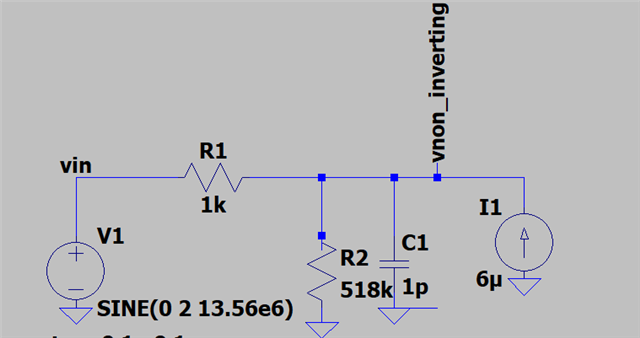

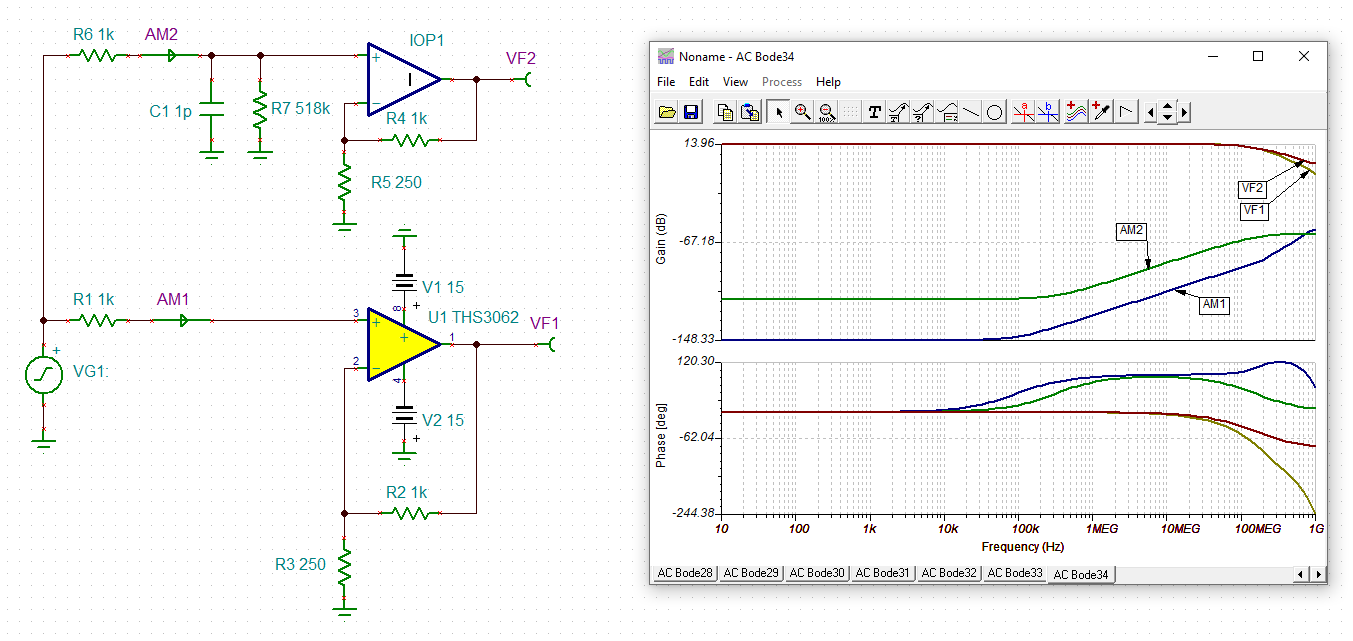

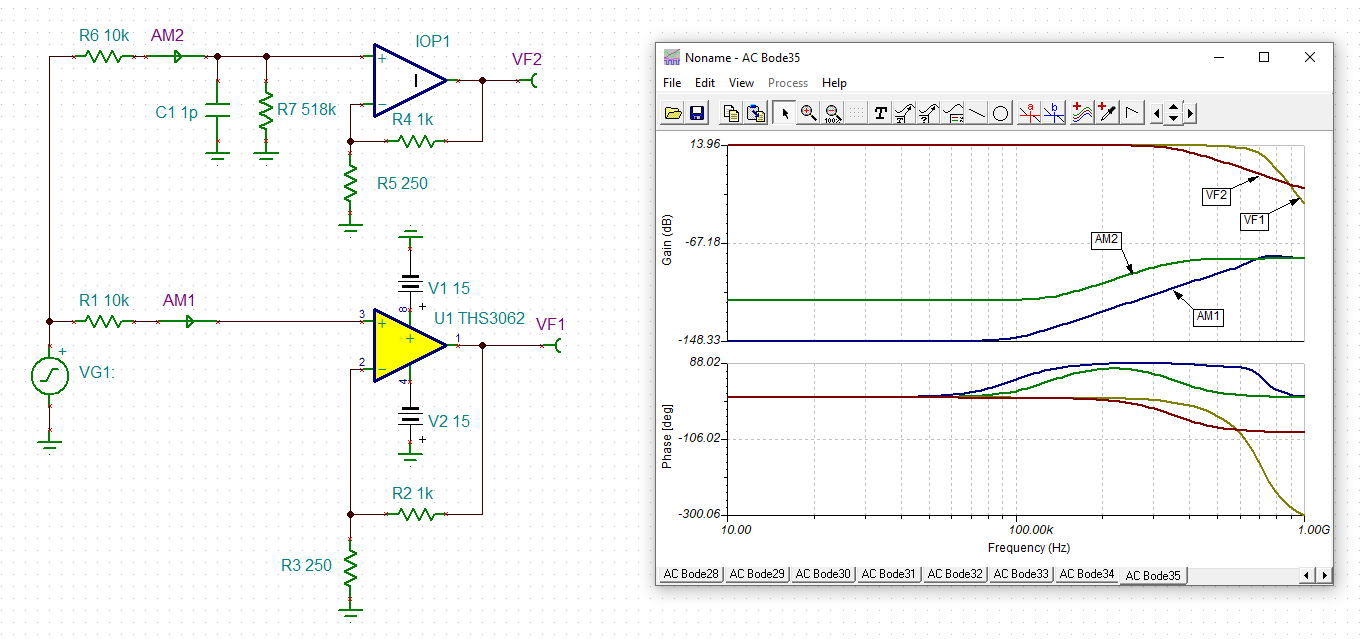

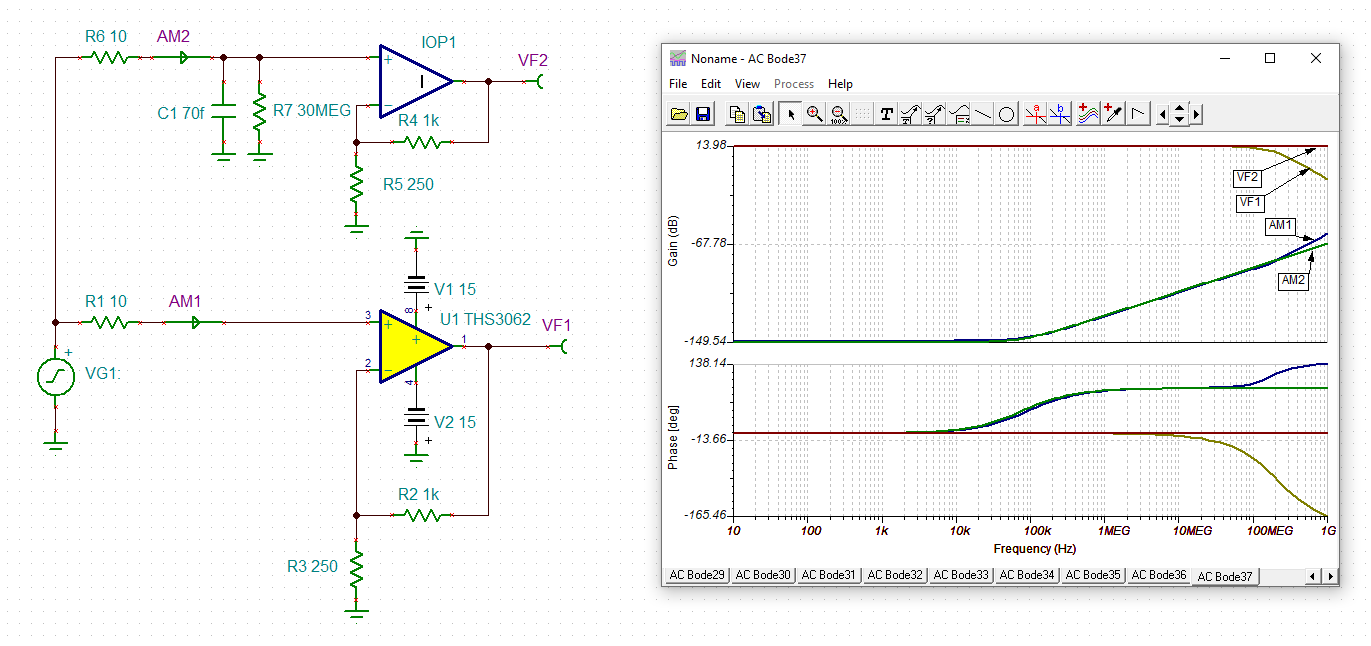

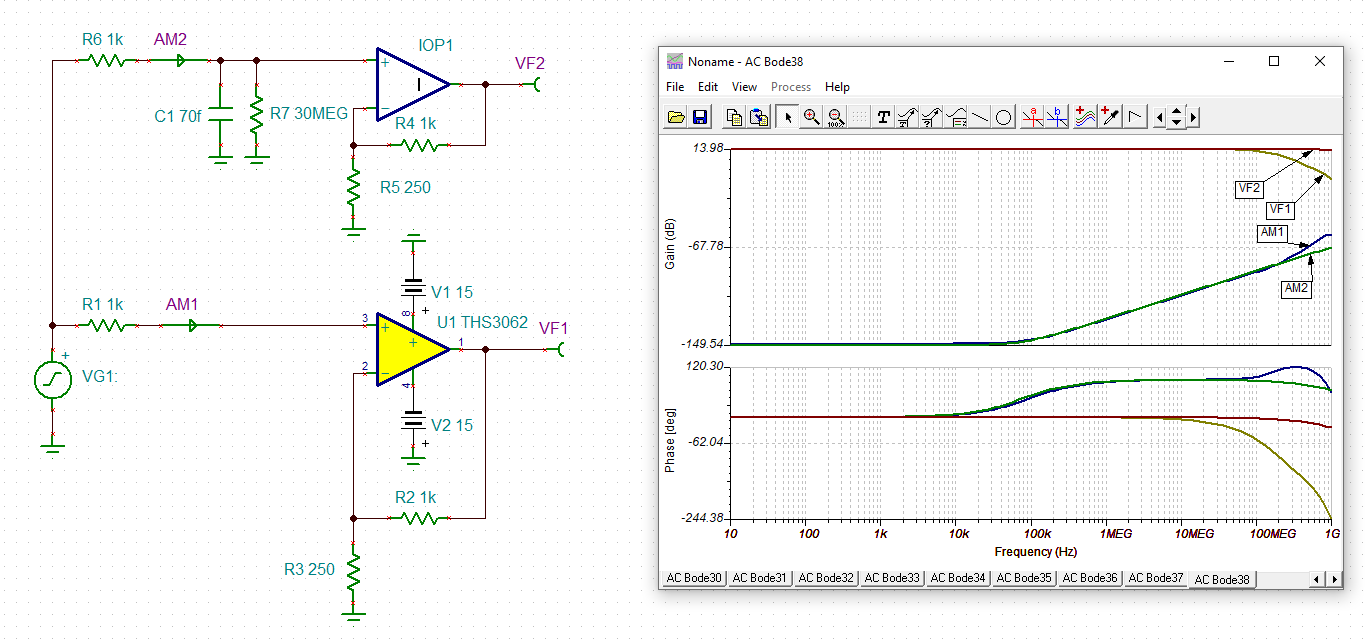

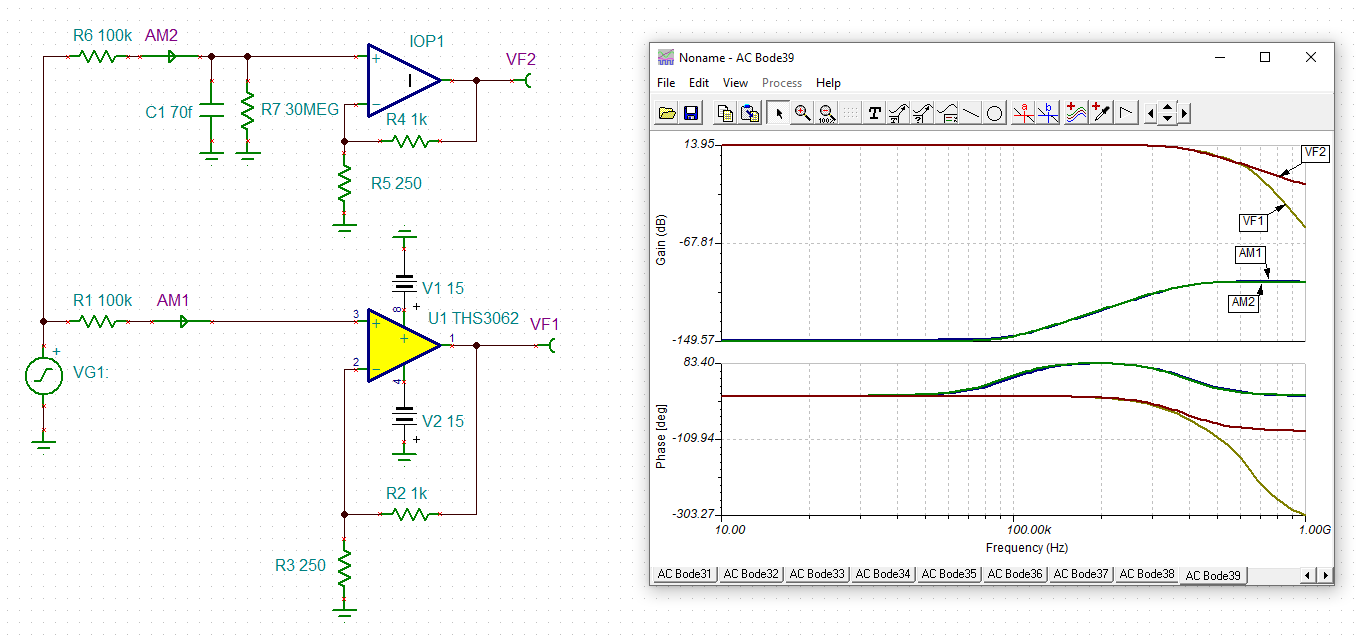

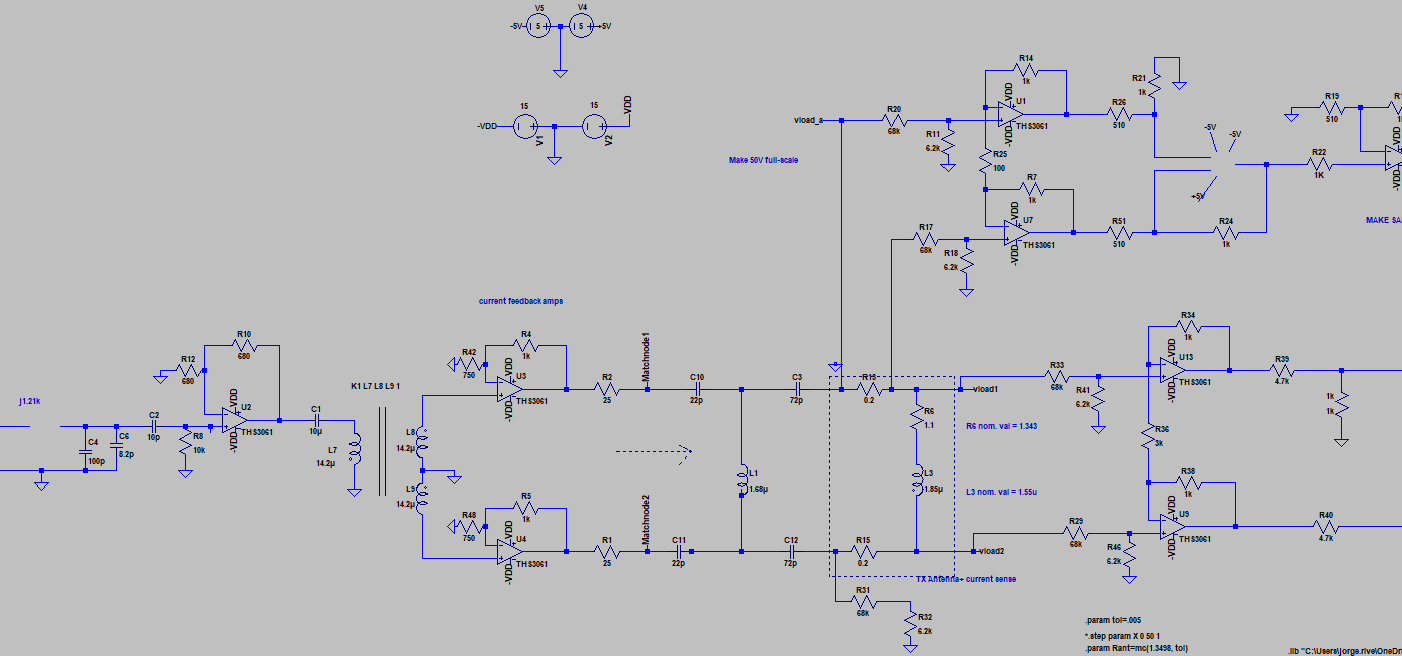

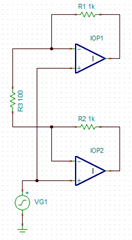

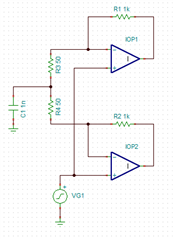

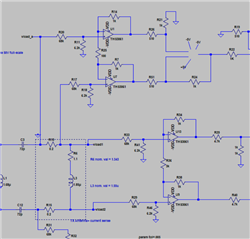

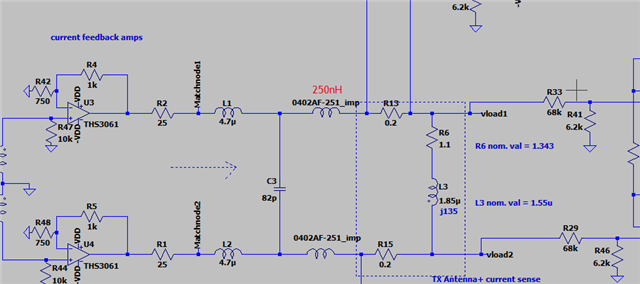

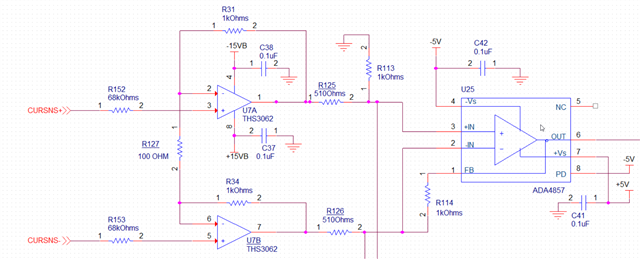

I have the THS3062 configured as an instrumentation op-amp as shown below:

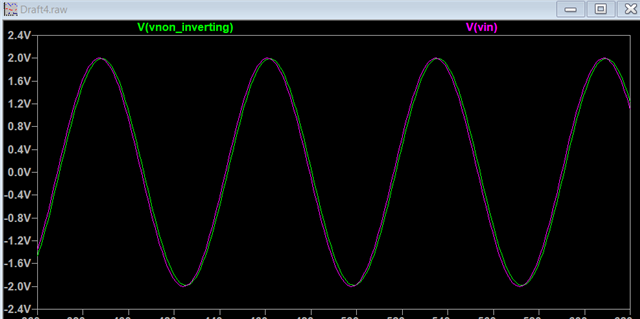

The currsns+ and currsns- inputs are a ~2Vp sinewaves at 13.56MHz.. I expect to see a slightly smaller, off-phase version of those signals at pins 3 and 5. Instead, I see what appears to be a 0.45V DC signal. What could be going on? pins 3 and 5 are high impedance inputs. I've verified power, layout, component values, population options, etc on the board. I'm stumped. Any suggestions as to what may be going on?

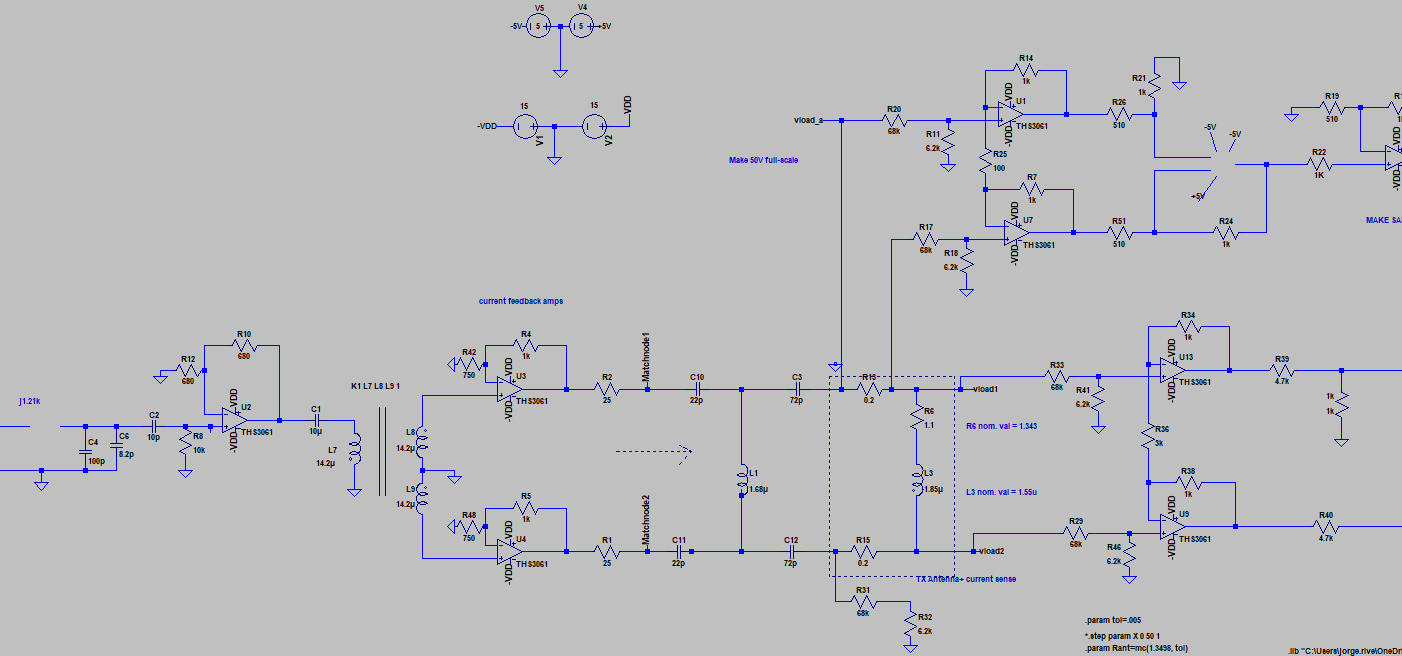

Simulation of circuitry works well.

Thanks,

Jorge