Other Parts Discussed in Thread: INA818, OPA320, OPA325, ADS8326

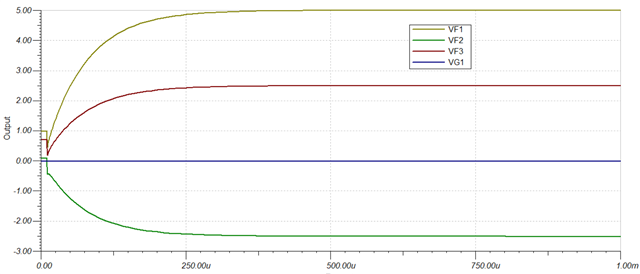

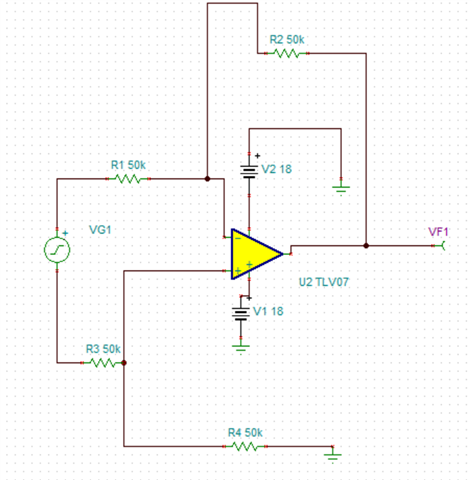

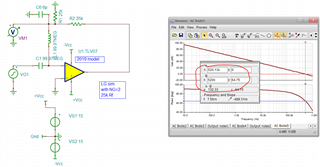

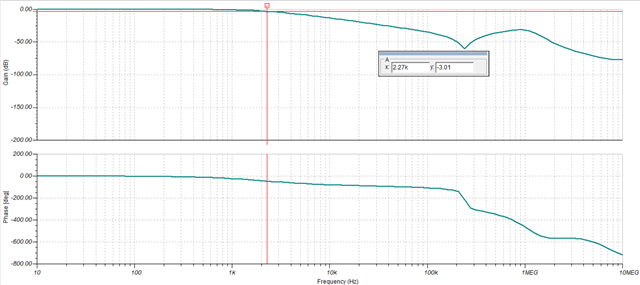

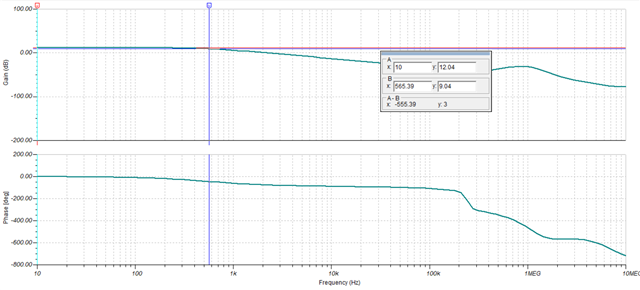

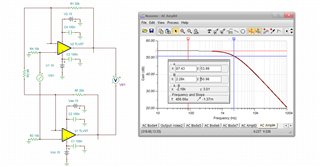

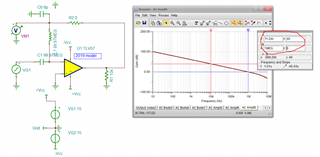

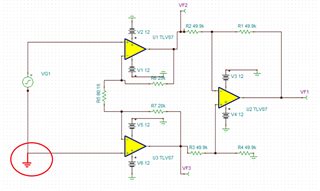

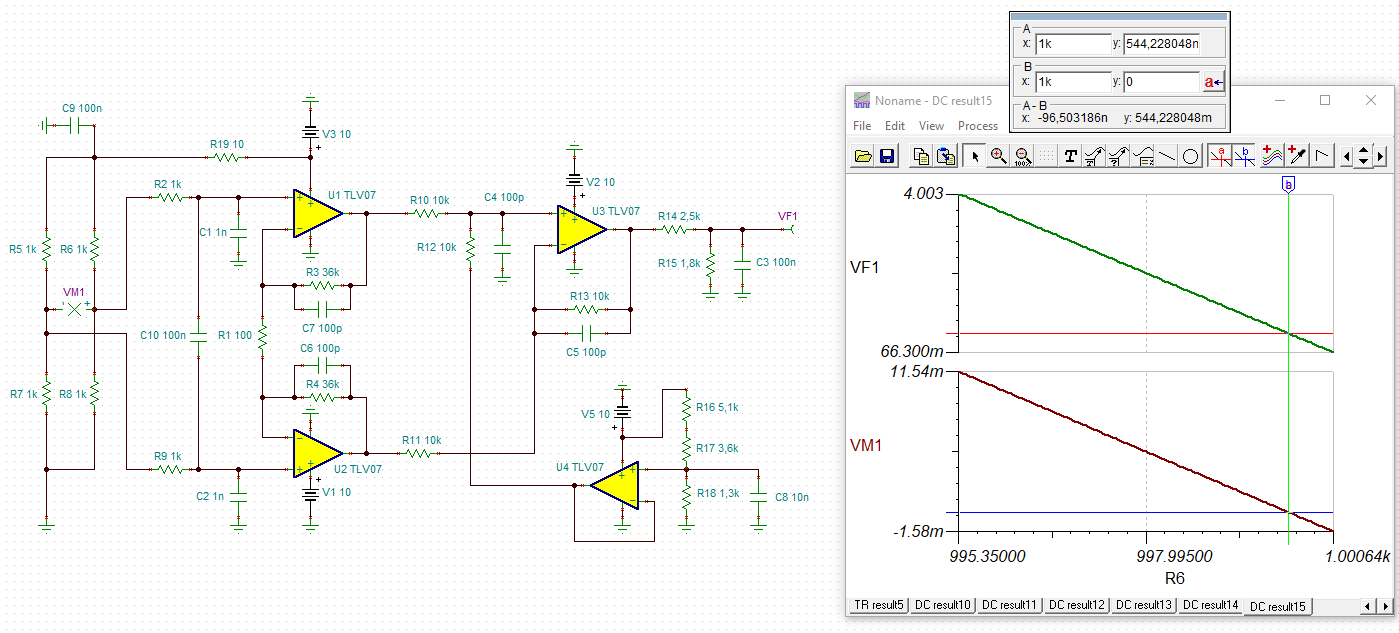

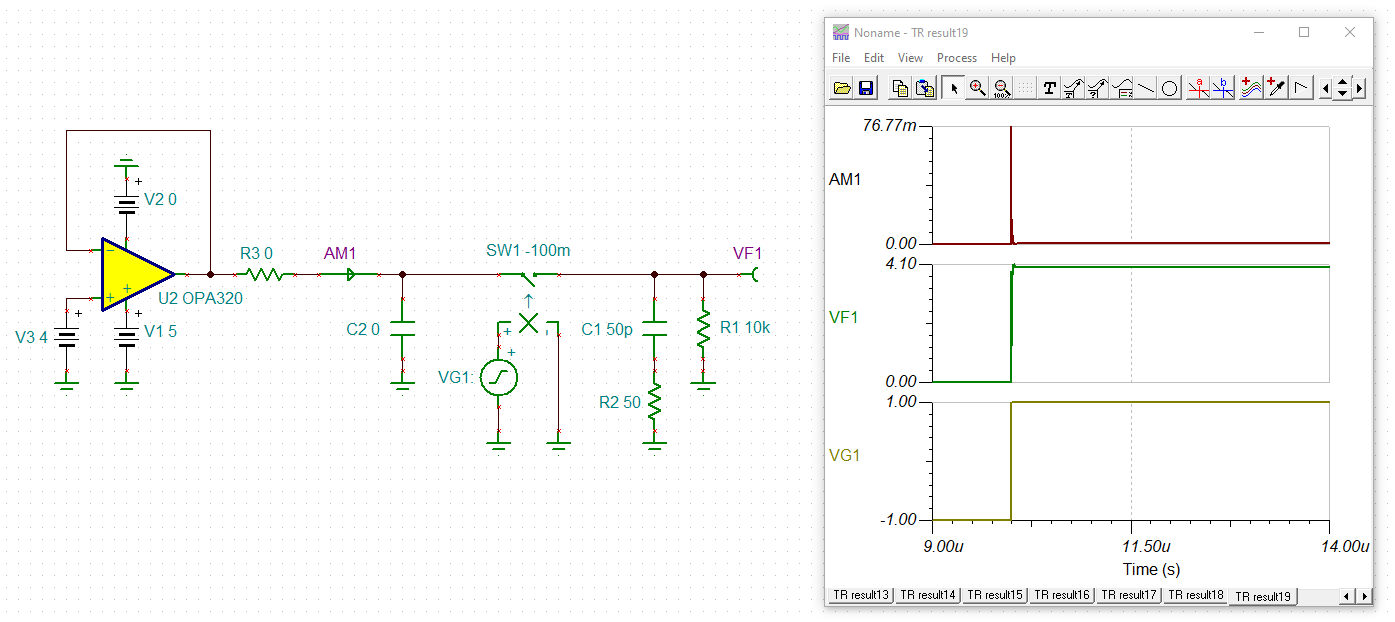

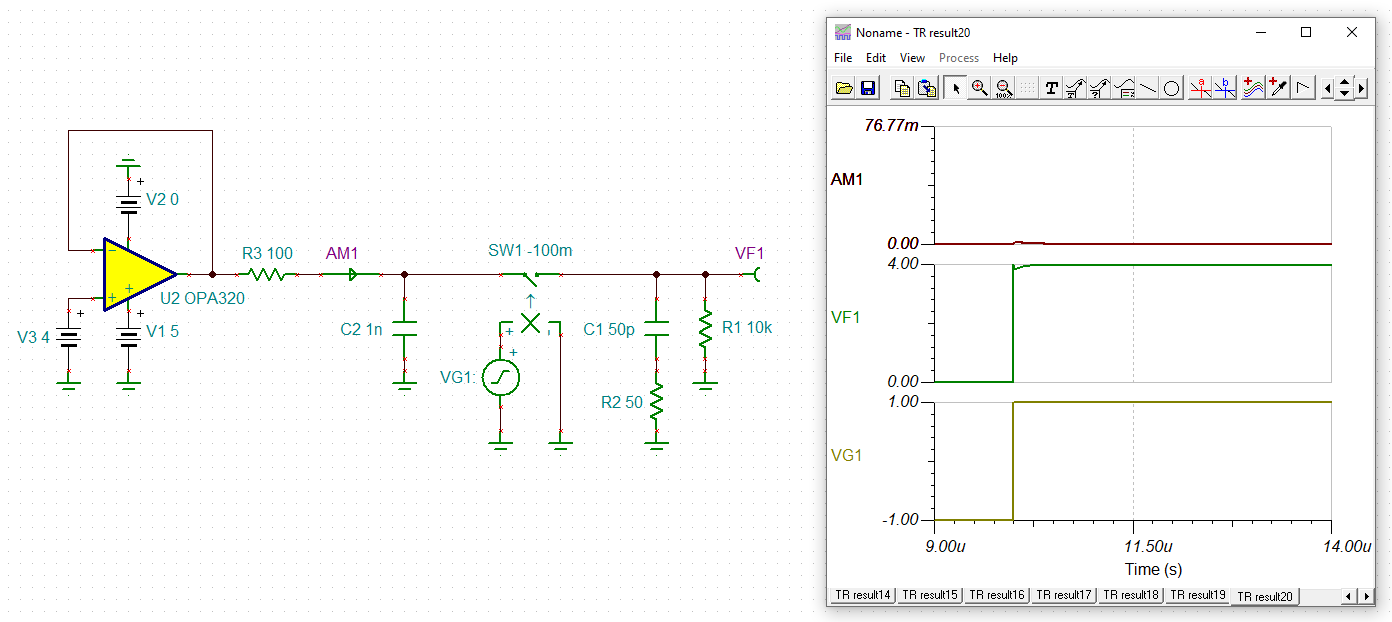

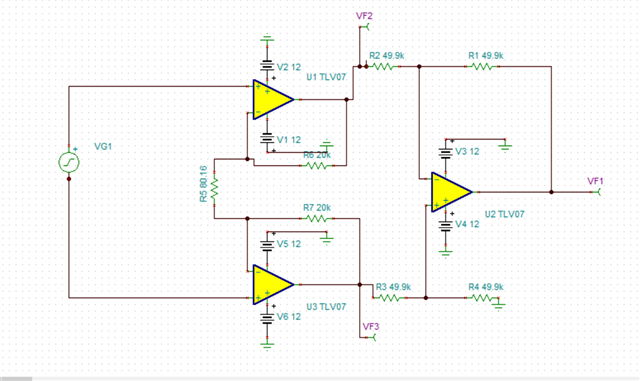

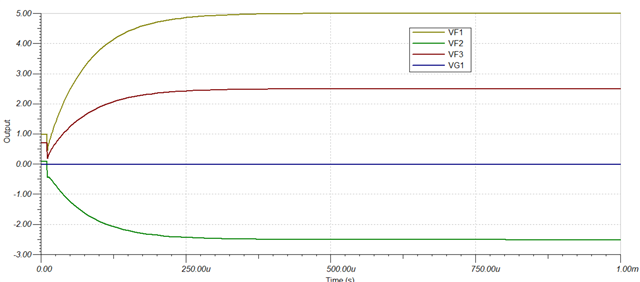

We are trying to implement instrumentation amplifier using tlv07 opamp to amplify 10mV signal 500 times. The circuit is something like this(the voltage source provides -10m step signal)

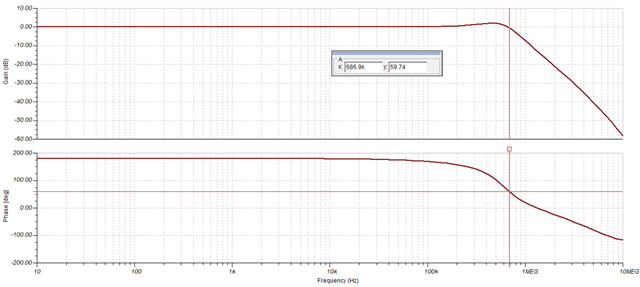

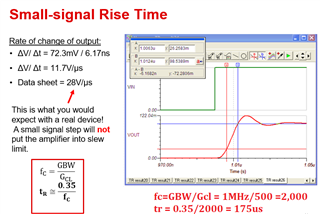

Why is the rise time so high (~0.250ms)? Is there a problem with the circuit? Or is there a problem with the op-amp, in which case request you to suggest a similar op-amp around the same price range. Also we want to implement INA using discrete opamp for research purposes, hence we don't wish to use INA chips. Any suggestions for improvement in the circuit are greatly appreciated. Thanks