Part Number: OPA657

Hi,

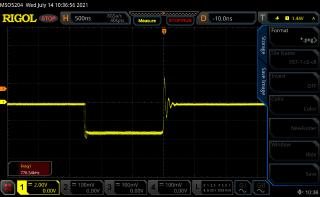

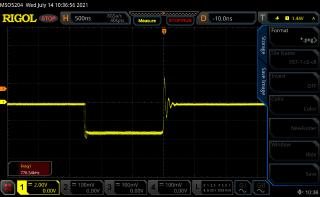

We use OPA657 circuit as TIA amplifier. Our output signal is on the following output.

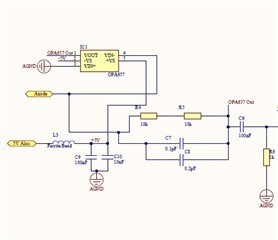

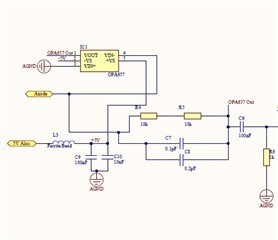

Our circuit is on the following picture

How can we prevent sinusoidal responses on digital pulse?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: OPA657

Hi,

We use OPA657 circuit as TIA amplifier. Our output signal is on the following output.

Our circuit is on the following picture

How can we prevent sinusoidal responses on digital pulse?

Well your closed loop response is peaking to give that step response overshoot and decaying sine wave, this just requires a tune on the feedback C, but that then requires an estimate of the source capacitance. keep in mind typical SMD R's (like your feedback R's?) have about 0.18pF parasitic themselves.

So,

I use 0.1pF on my circuit plus 0.18pF for the Rf resistor. Totaly 0.28pF. ICan the total capacitance caused this effect? How can i reduce this effect?

The detector capacitance and the feedback capacitance must fit together.

What is the detector capacitance of your APD?

Kai

Thanks, so keep in mind there is often a capacitance vs reverse bias curve - we want the C at your intended reverse bias voltage - but working with that 95pF for now, to hit a closed loop Butterworth with the OPA657 and 20kohm gain you need a feedback C of 1pF total and would get an F-3dB of 11MHz. The Butterworth will overshoot about 4% and ring a little, but should be better than you measure now.