Part Number: OPA333

Hello,

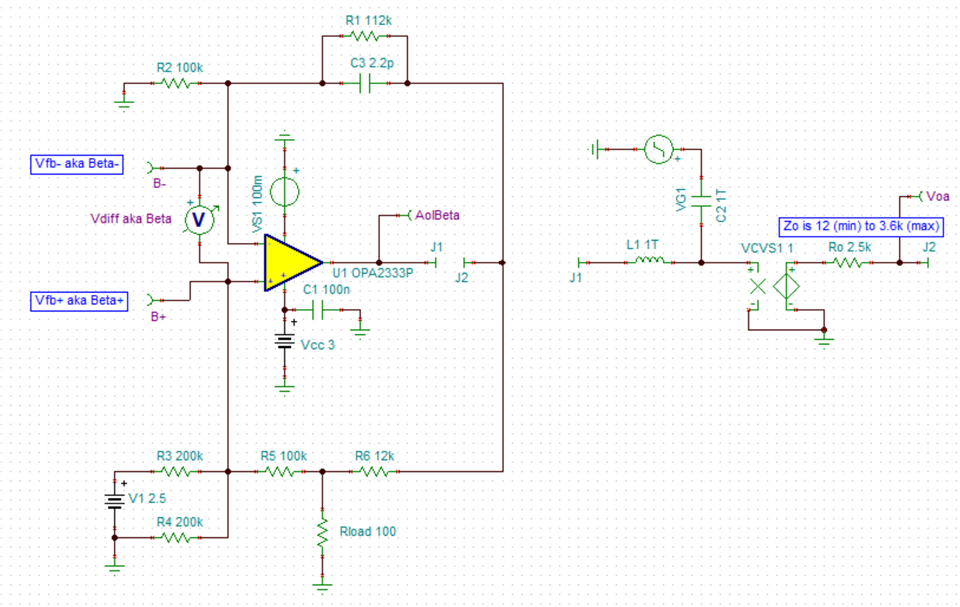

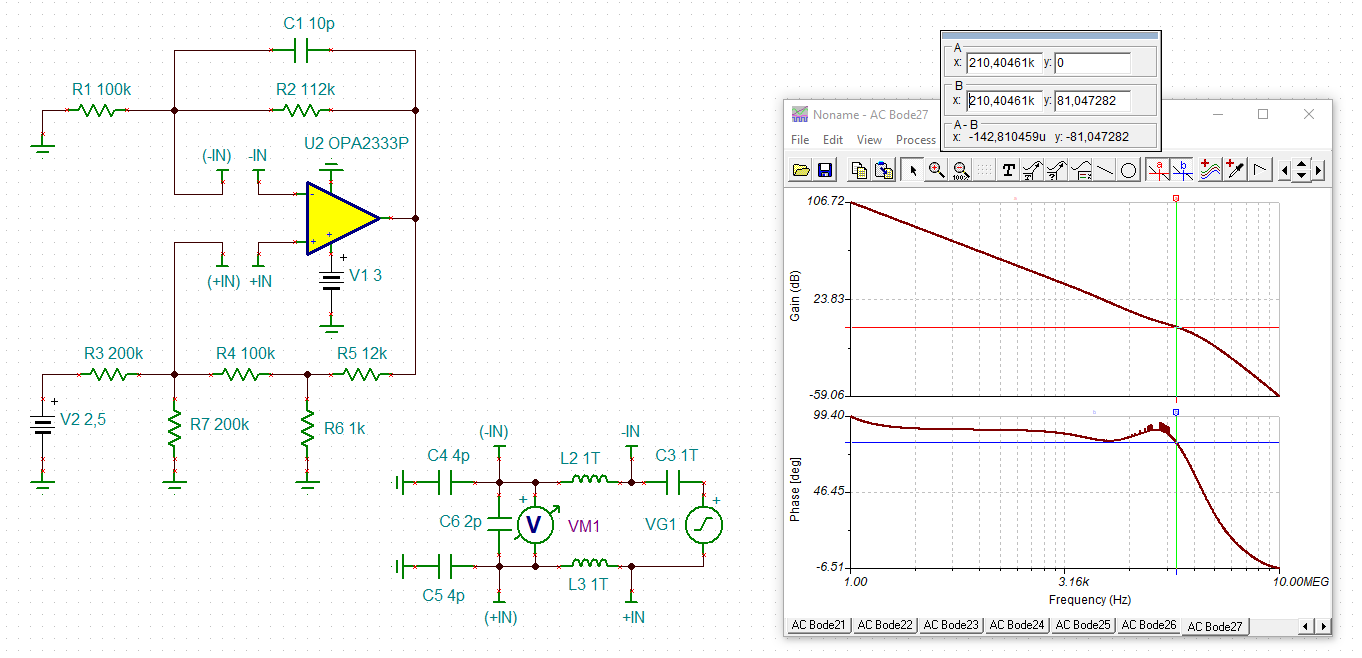

I've been using an OPA333 as a low-power, low frequency Howland Current Source - generally it works quite well but I'm finding a small amount of oscillation creeping in at an ADC further down the processing chain so I'd like to do some stability analysis on this current source as I have reason to be suspicious that this might be the source. Schematic of relevant section is below:

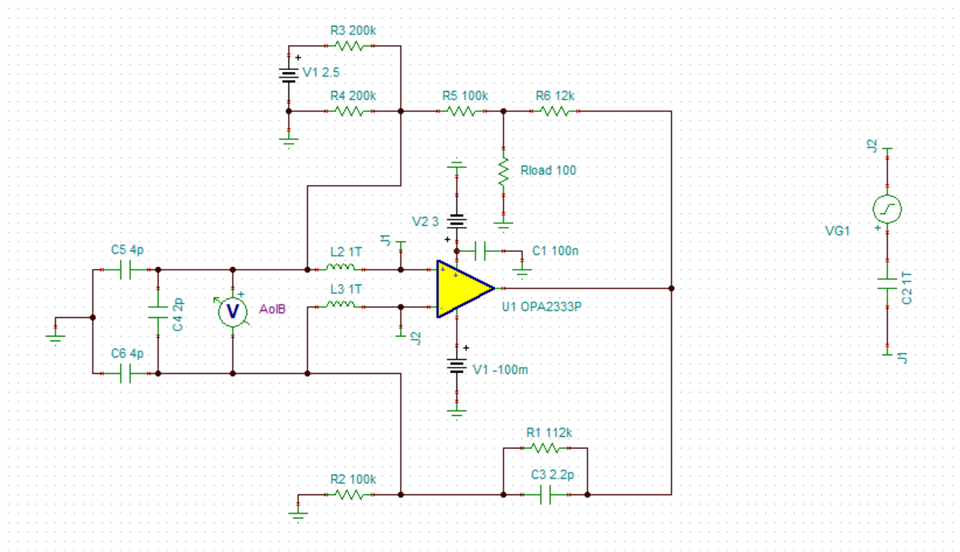

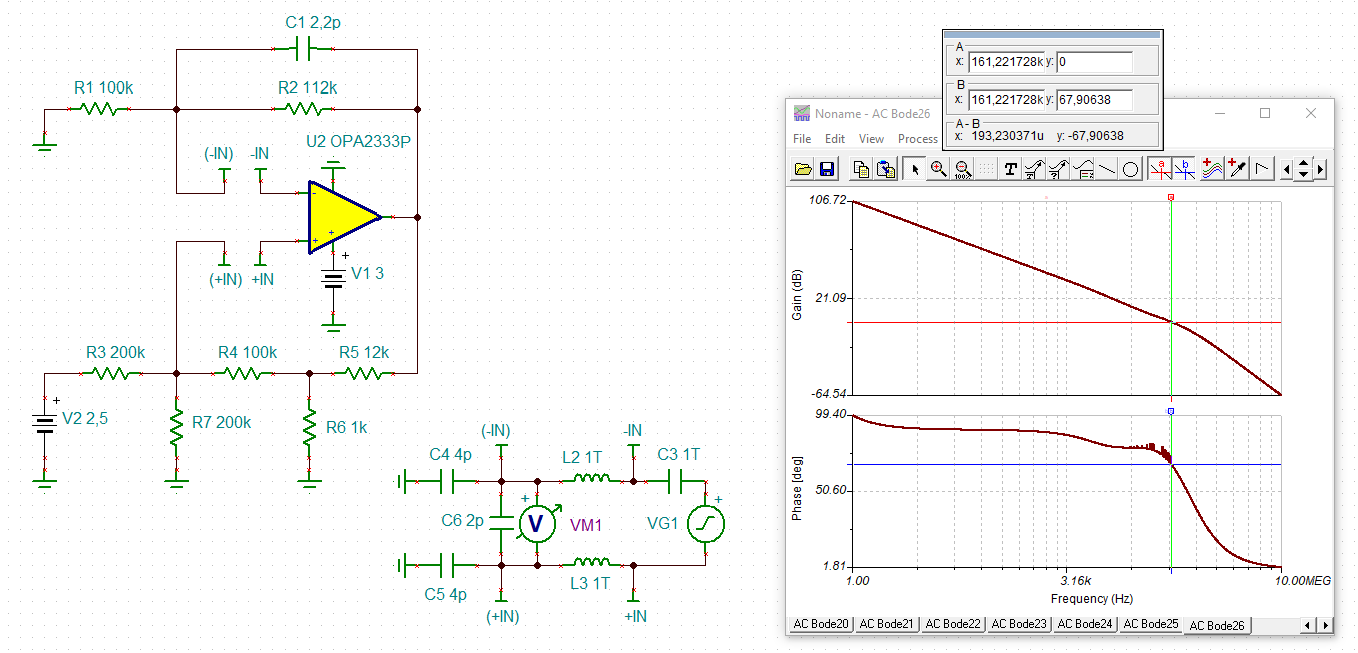

I've used Collin Wells' material on stability a few times in the past and found it very useful, particularly the sections on how to break feedback loops in TINA Spice simulator to see how it looks in open-loop. However, this time I'm not quite sure where to start, as there are both positive and negative feedback loops. Any suggestions on what I can do here?

Thanks,

Gordon.