Part Number: OPA4322

Other Parts Discussed in Thread: TINA-TI

Hi OPAMP folks,

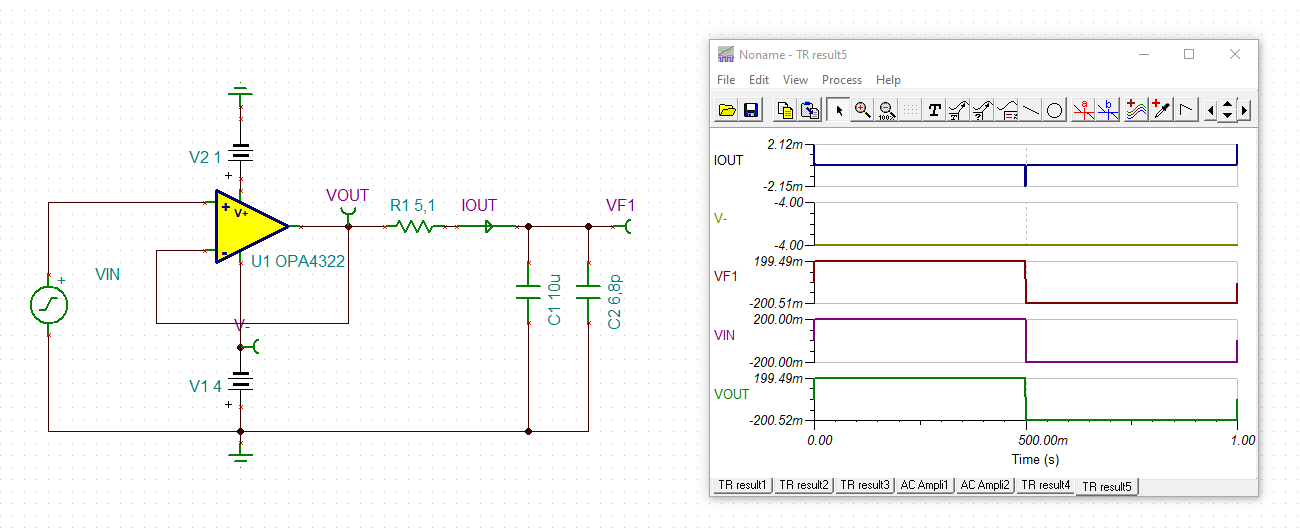

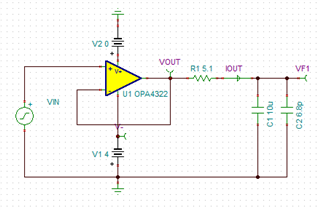

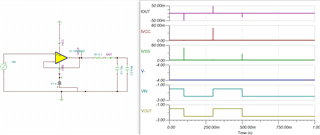

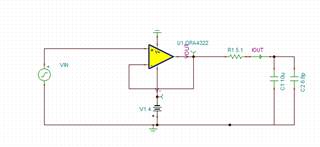

I'm doing TINA simulation with OPA4322 as an unity gain buffer. Could you help advise for its operation?

What I'm trying to do :

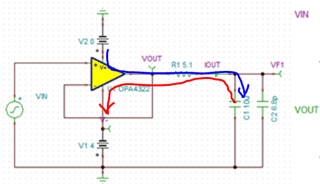

I want to implement an unity gain buffer (DAC output buffer) with OPA4322 to see how much of current is drawn from voltage supply during the DAC value change.

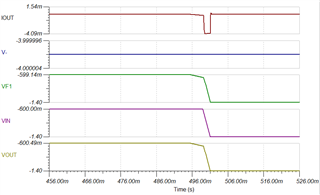

Condition :

- Positive supply rail : GND

- Negative supply rail : -4V

- DAC variation (△Vin) : 0.4V or -0.4V

- Cload and Riso : 10uF and 5.1ohm

I configure the circuit as above. And I have questions as below from the simulation result.

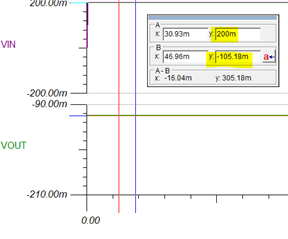

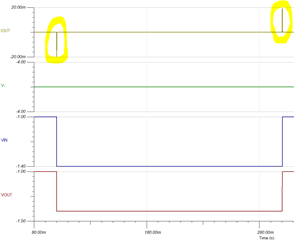

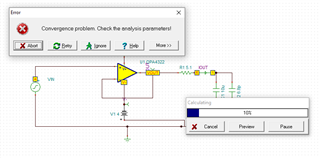

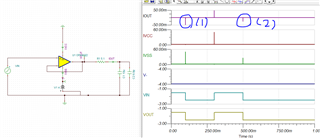

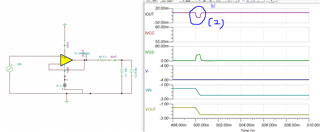

(3)

It looks the the unity gain buffer does not operate normal. As it's a voltage follower, I thought VOUT should follow the VIN. Is there anything wrong in circuit?

(1) 1.

Per my understanding, V- is supposed to stay in -4V under any circumstance. But it's not -4V during VIN = 0, and it's not -4V also during VIN=-0.4V. Could you advise why the V- node is not stable on -4V?

(1) 2.

Moreover, I do not understand how V- changes from -3.32V to -2.92V when VIN changes. Could you explain the mechanism?

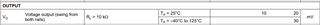

(2) 1.

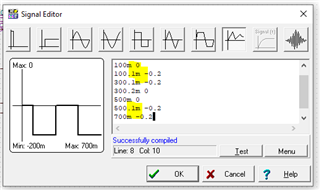

Per my calculation with the basic capacitor equation (I = C* dv/dt), 4mA of the instant current is required to charge 10uF capacitor on output.

I = 10uF * 0.4V/1ms = 4mA (1ms is set by myself from the input signal. Please find the VIN setting.)

But the simulation shows 2mA only. Could you advise why?

Thank you.