Hi,

I'm unsure what would be the optimal solution to place a INA240 for lowest noise for the current measurement.

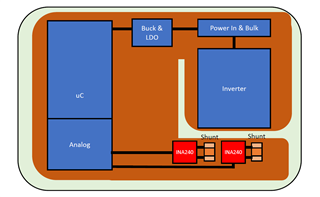

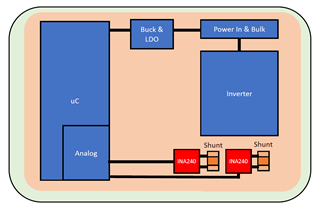

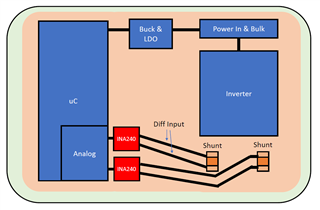

I'm using two INA240 for a motor control application and would like to get the optimal performance out of it. I'm using one solid GND plane for the whole board and separte the analog and digital signals by spatial serparation. Now I would like to know, where I should place the INA240 on the board, since I already saw different designs with different variants, where the INA240 is close to the shunts or where it is close to the ADC.

From my point of view it makes the most sense to place the INA240 near the ADC and route the differential pairs to the shunts to remove the low frequency current influence from the Inverter on the GND pin of the INA240 and the OUT signal is only single-end and prone to noise. From a EMI point of view, it would probably be better to have the differential pair close to the shunts, to remove the antenna length for the HF PWM signals.

1.) Directly placed at the shunts and loop the output back over the board to the ADC

2.) Placed the INA240 close to the ADC input and loop the differential pair to the shunts

So my questions are:

1.) What is the best placing solution for lowest noise of the INA240?

2.) Is the return current for the IN+ the IN- signal or the GND? For me it looks like it is the GND, since a OPAMP is integrated.

3.) Is a LPF recommended on the OUT pin of the INA240 to reduce noise and how much larger should be the cut-off frequency than the sampling frequency? 20dB?

Kind Regards,

Sebastian