Other Parts Discussed in Thread: OPA695, TINA-TI

Hi

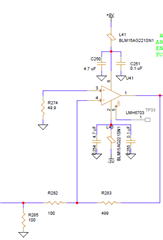

I need to drive the LMH6703 in the SOT-23-6 package from a CML output.

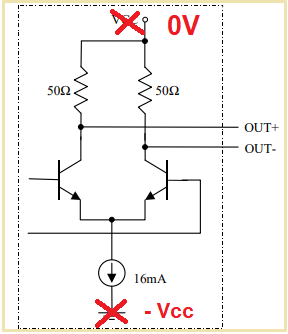

The CML gate will operate from negative supplies, so the output is internally terminated 50 ohms to GND

The CML output will preferably be DC coupled to the OPAMP circuit.

GAIN 5 or 6

My prime interest is rise time 0%-100%. I don't mind slight overshoot.

The goal is a positive going pulse at the opamp output. I can use the positive or the inverting output of the driving gate (the other output terminated to 50 ohms of course), so I can choose gain polarity of the opamp circuit.

Is it preferable to use the inverting or non-inverting configuration? What will give me the faster rise time, and what will give me the faster slew rate?

Also - will the OPA695 give me better or worse performance for this design?

Thanks

Pinhas