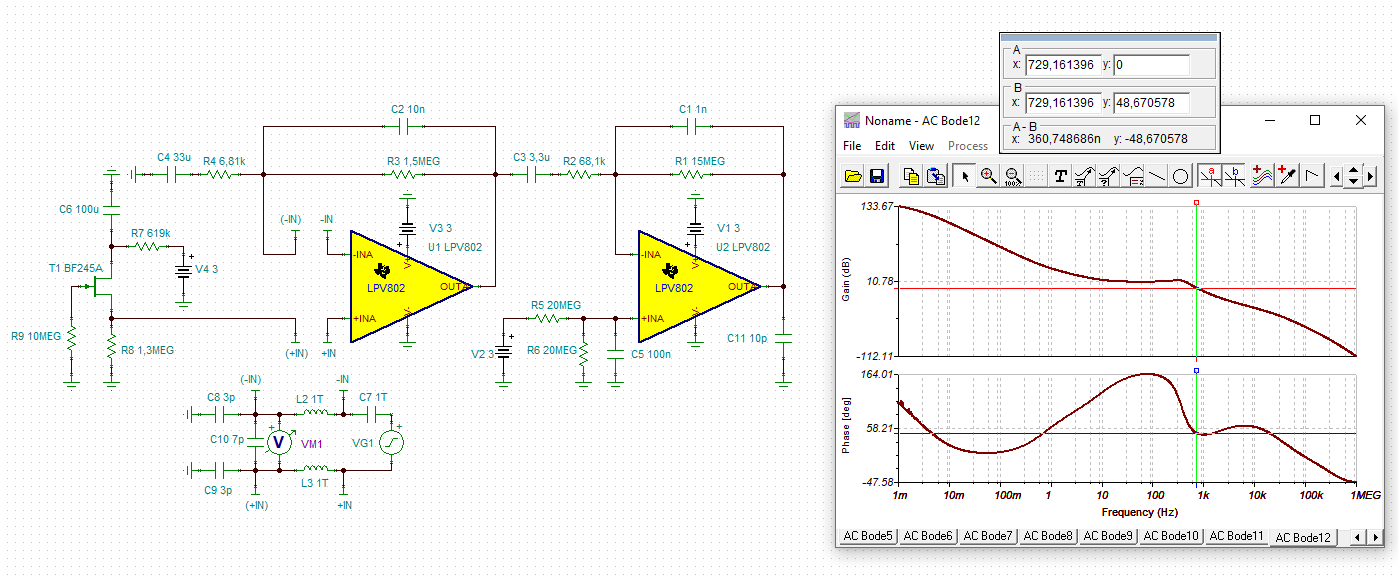

Other Parts Discussed in Thread: TIDA-00489, LPV802

Hello.

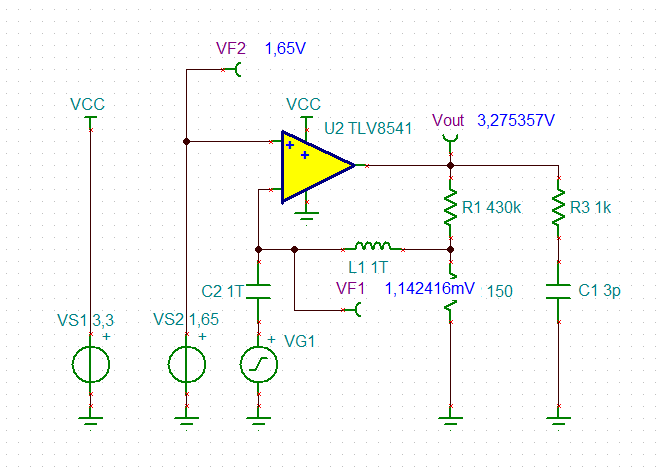

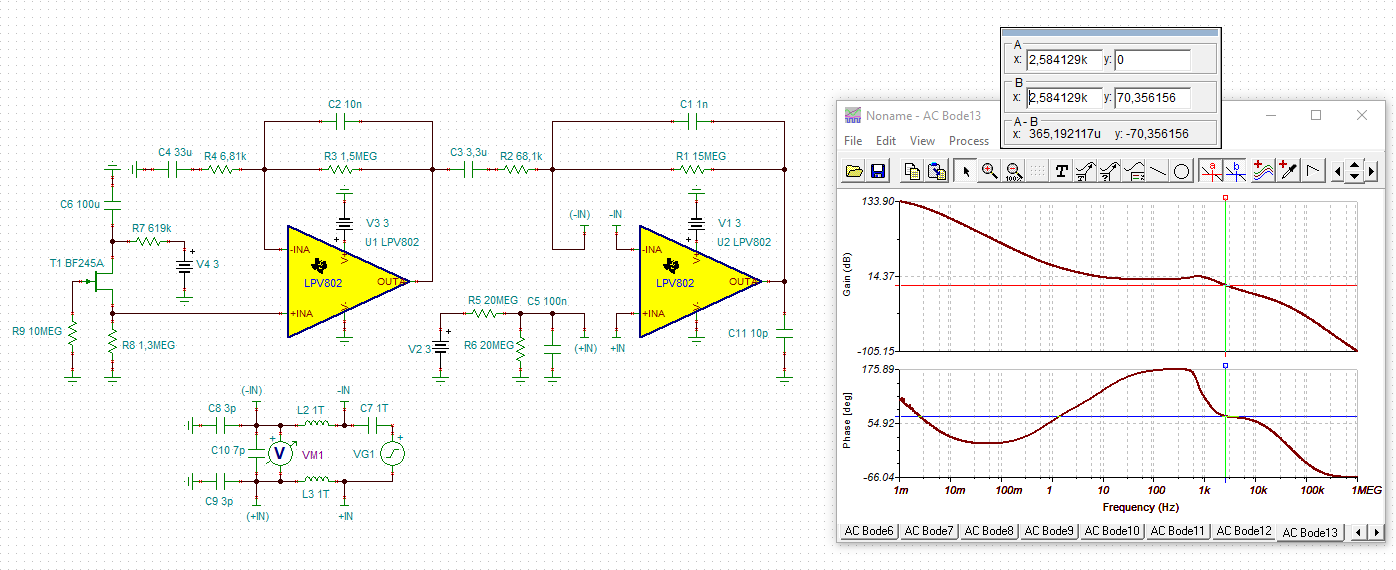

I'm attempting to prove that this noninverting amplifier circuit is stable using the method outlined in https://training.ti.com/ti-precision-labs-op-amps-stability-spice-simulation?context=1139747-1139745-14685-1138805-13850.

TLV8541_Stability_Simulation.TSC

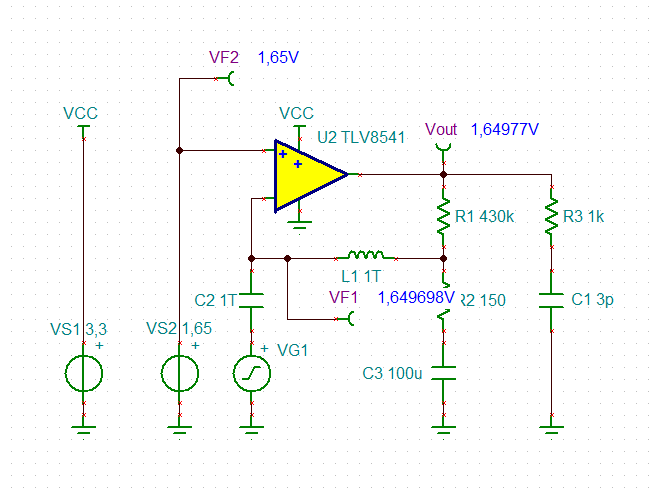

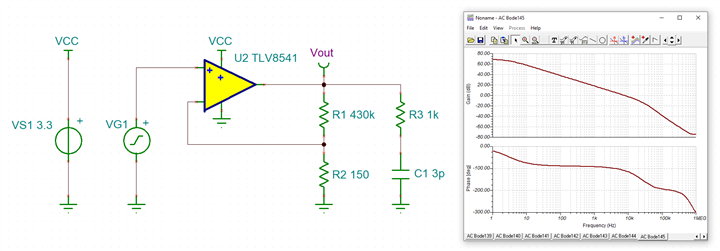

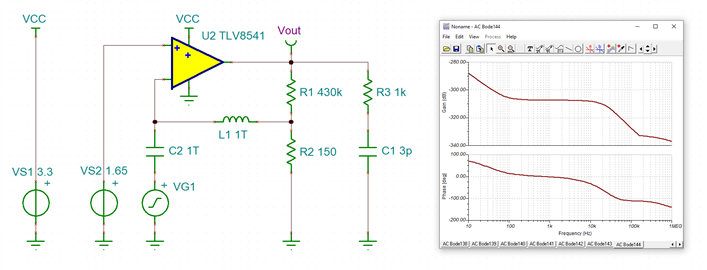

When I adjust the circuit to isolate the feedback components, the gain dives well below -280dB. This makes sense given the voltage divider, but makes it impossible to assess the phase margin at 0dB.

TLV8541_Stability_Simulation-modded.TSC

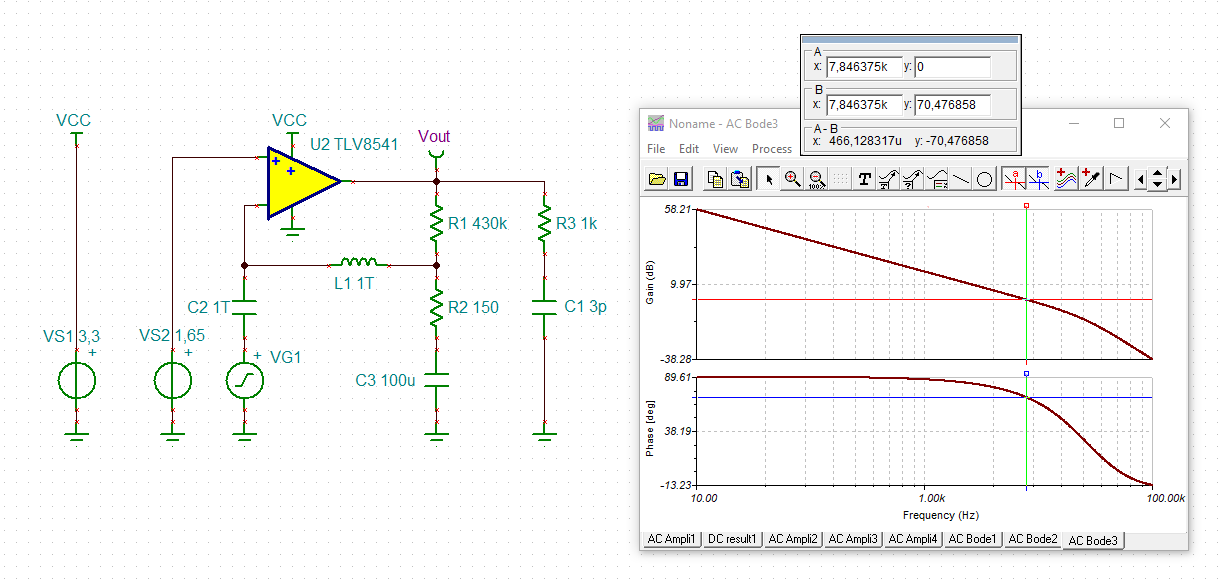

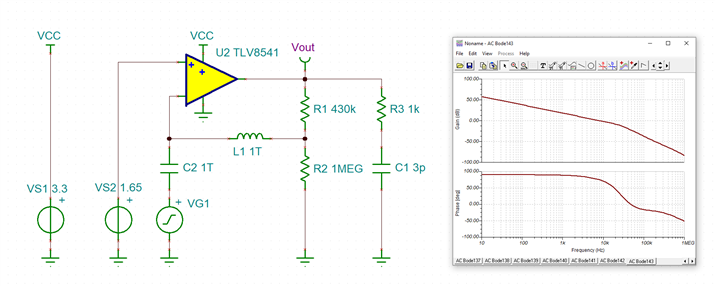

If I increase R2 to a large value, the gain information becomes useful.

1. Is this method only valid if there is no voltage divider in the feedback loop?

2. Is there are better or more accurate way to simulate stability for this circuit?

Thanks.