Other Parts Discussed in Thread: OPA855, LMH5401

The layout guidance provided in the OPA855 data sheet is to remove ground planes under all input an output pins.

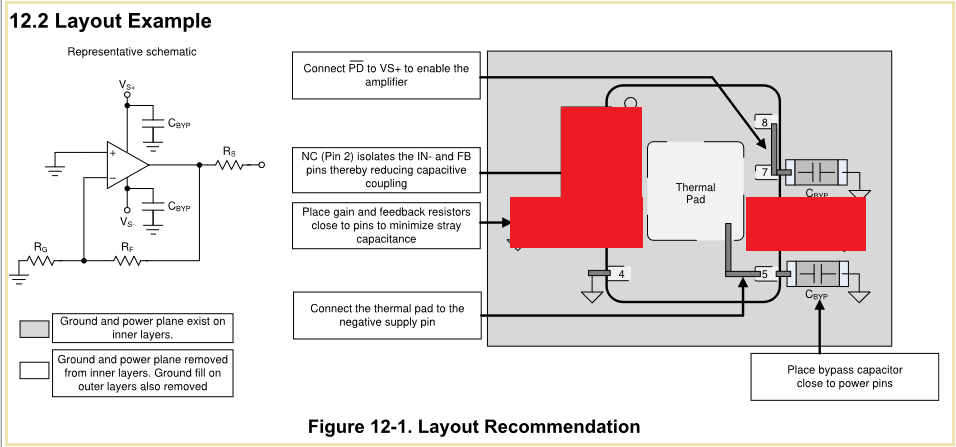

The Figure below the text only shows a cutout in the region of the FB pin only.

Should the actual output pin also have the cutout to reduce parasitic capacitance?