Other Parts Discussed in Thread: CC3220MOD, , TINA-TI, XTR115

Hi,

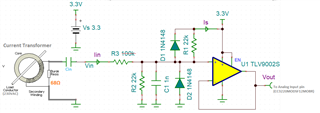

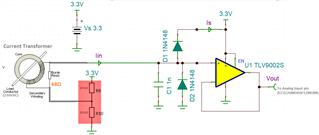

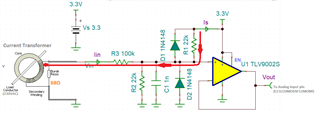

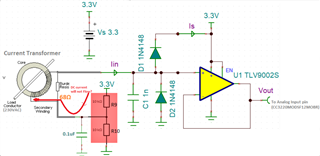

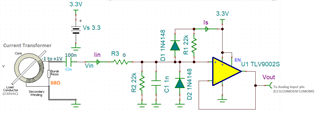

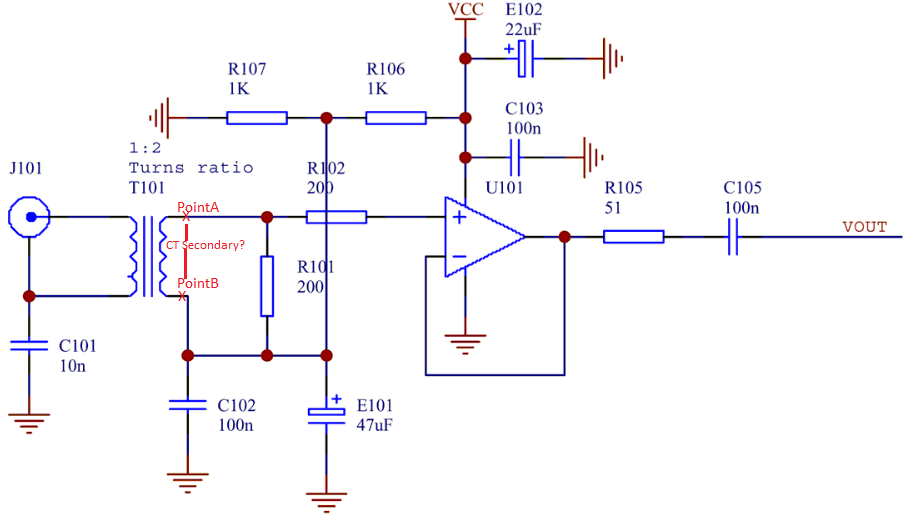

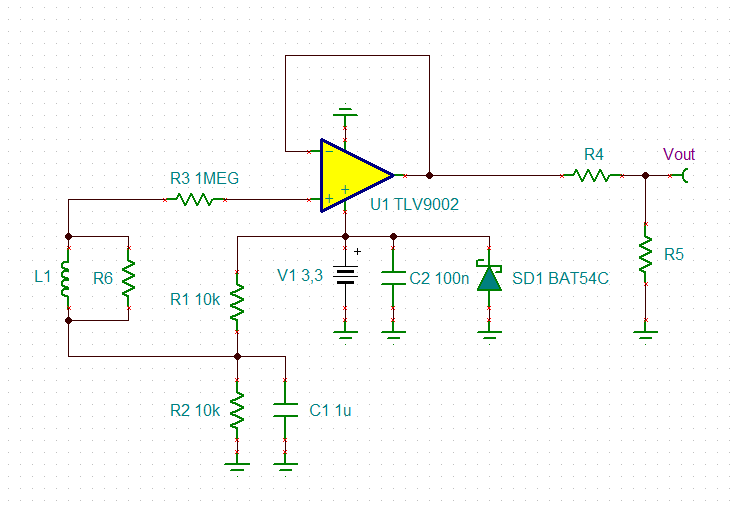

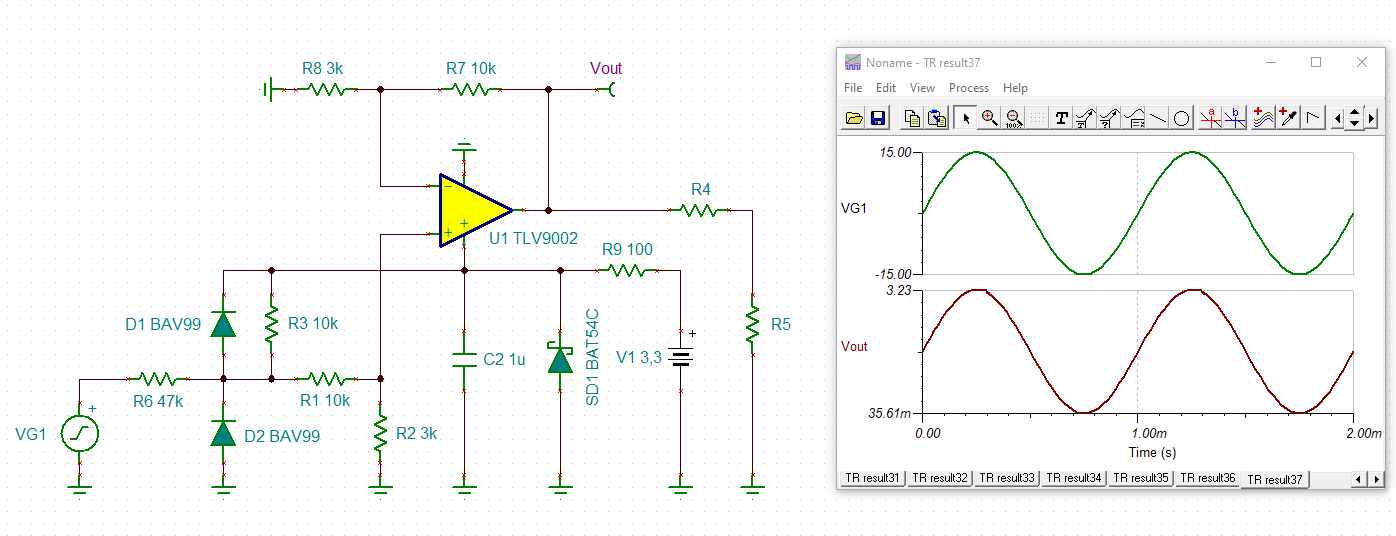

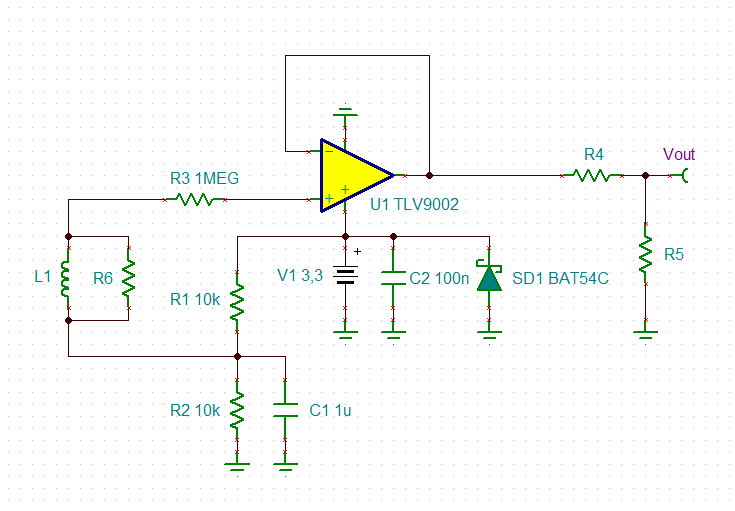

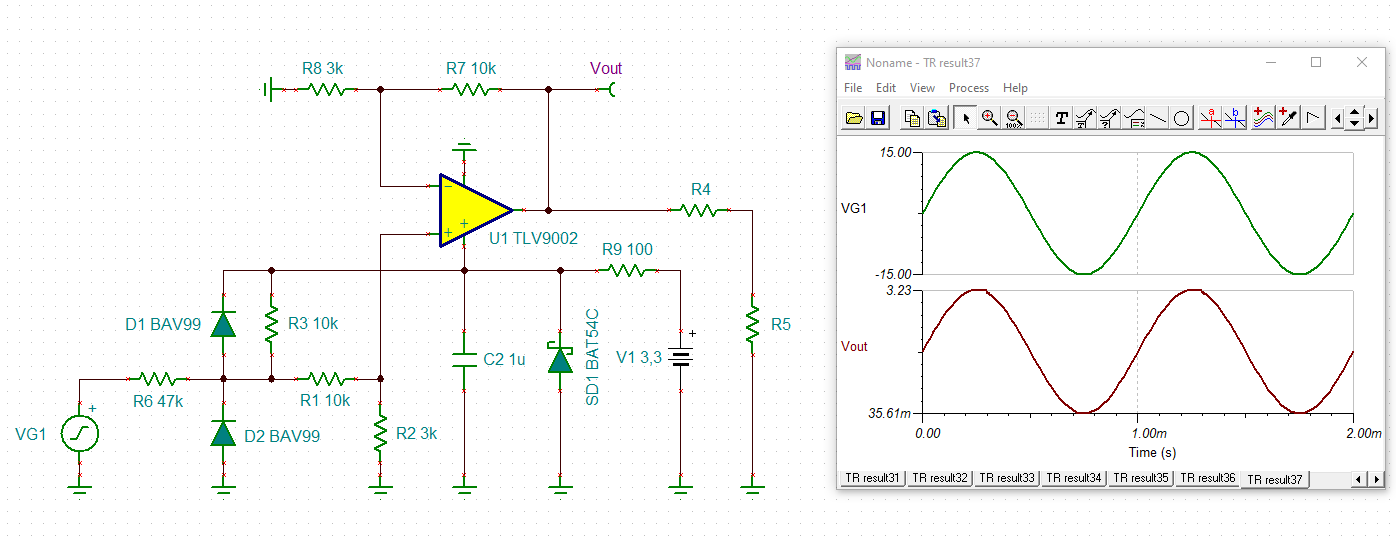

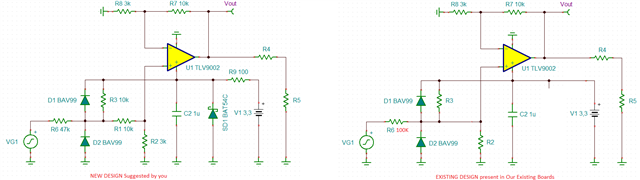

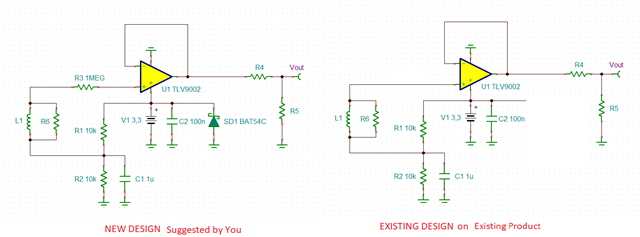

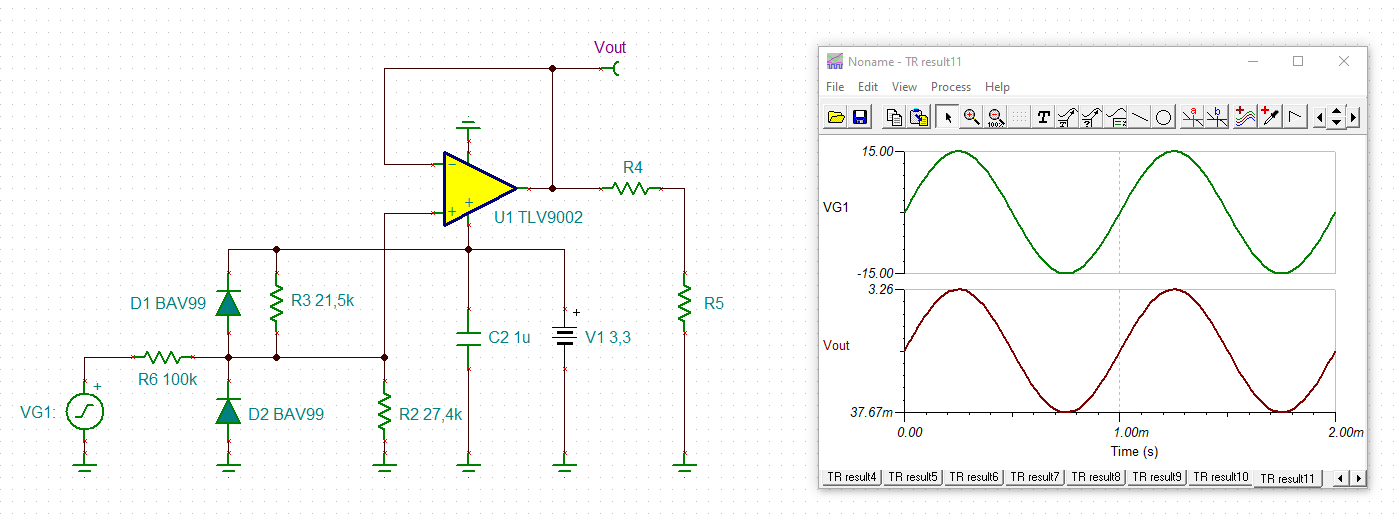

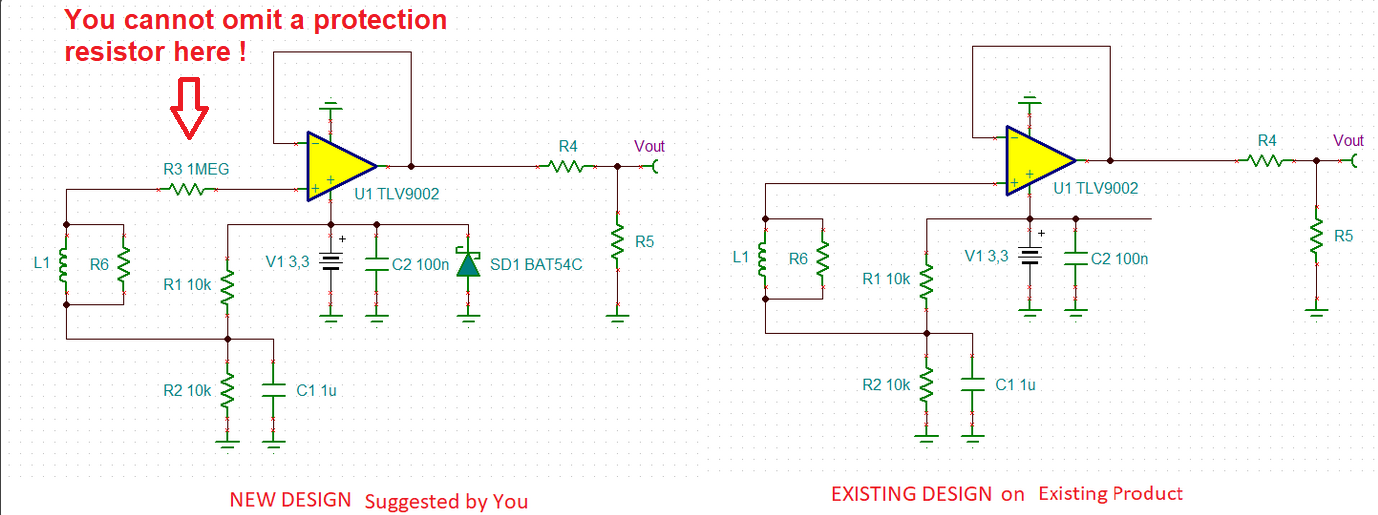

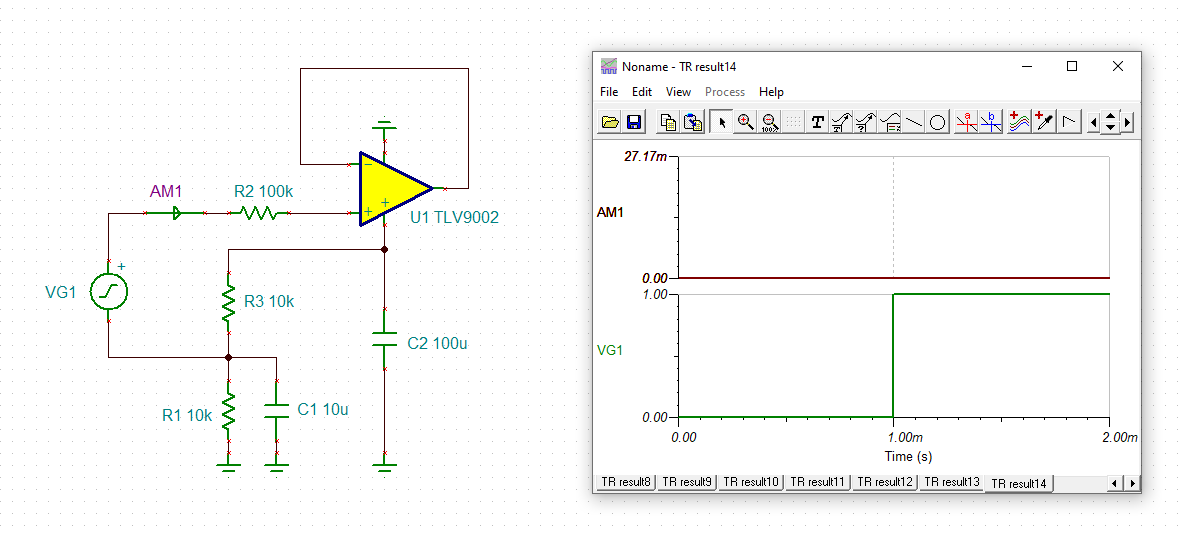

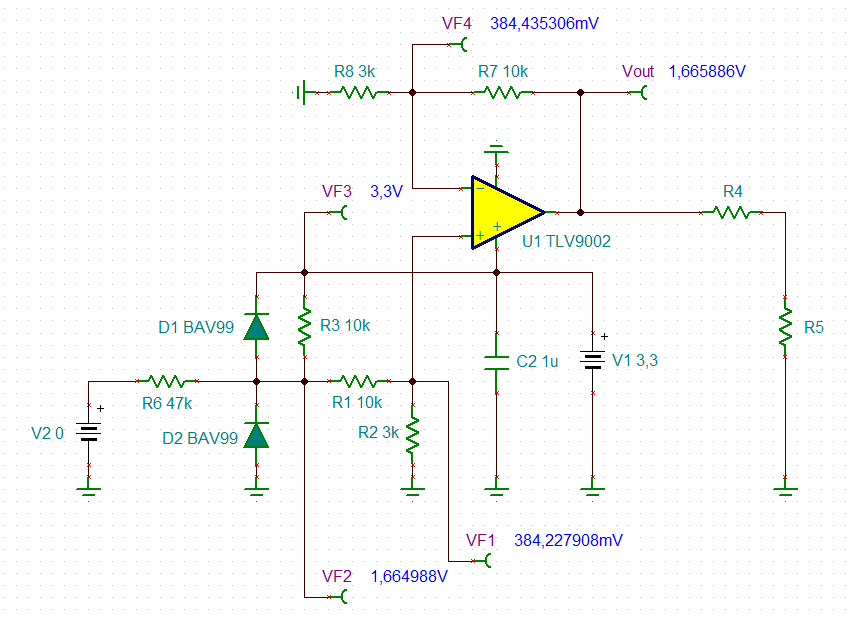

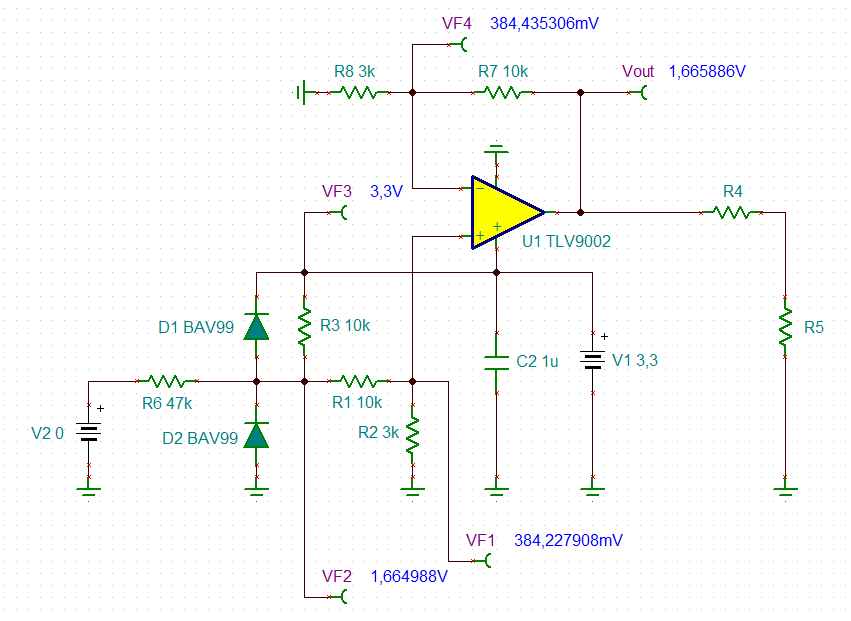

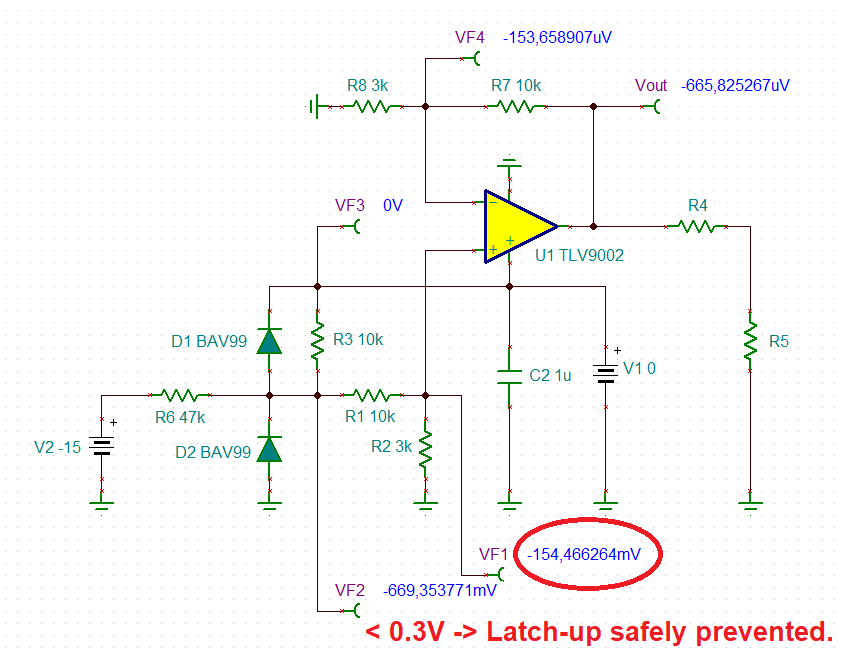

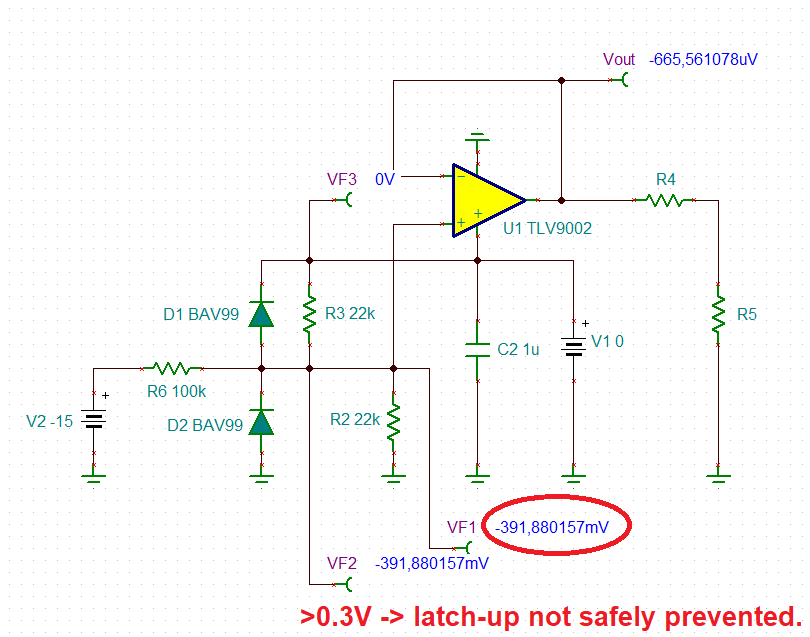

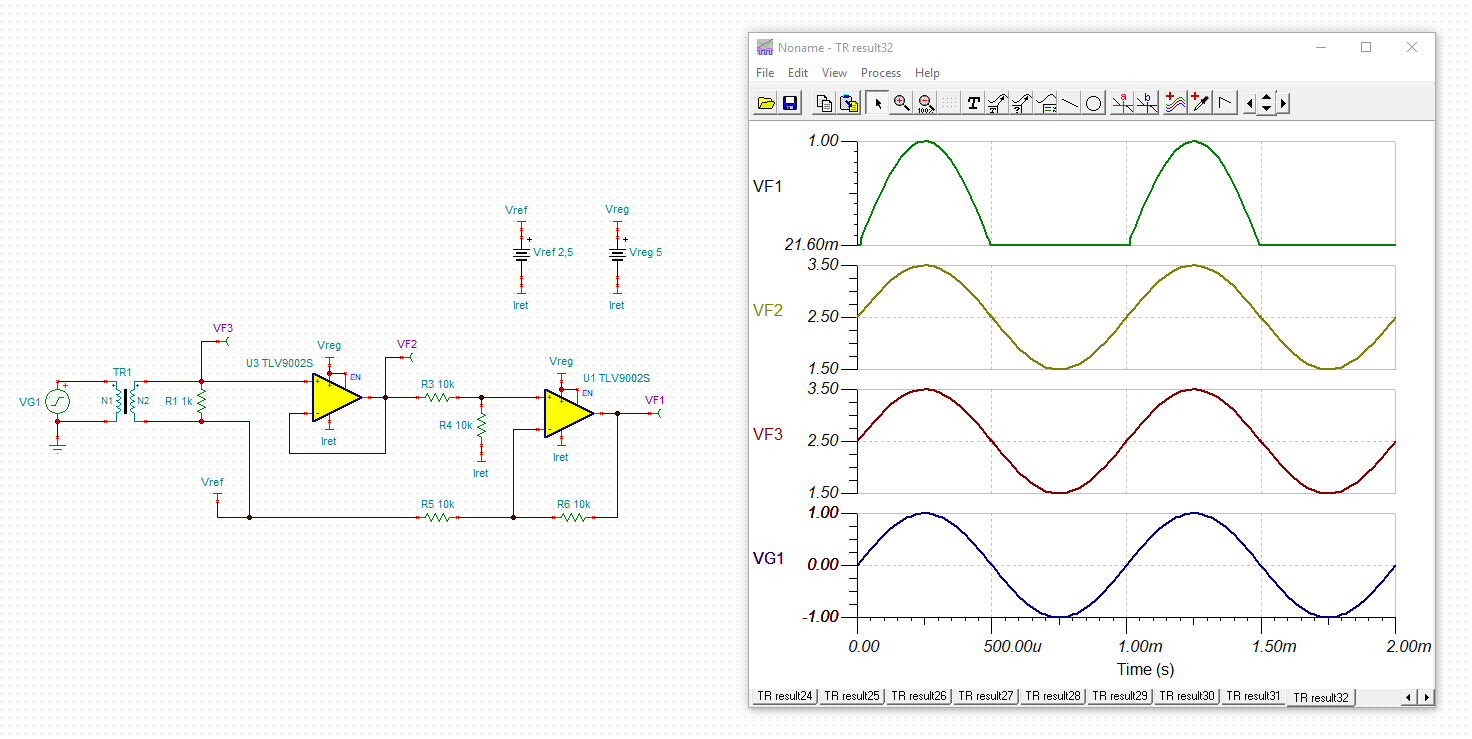

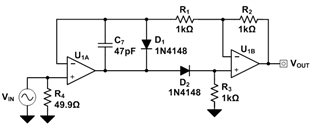

As suggested for the last post from Ron Michallic, below schematic is working fine for the input voltage range from -15V to +15V.

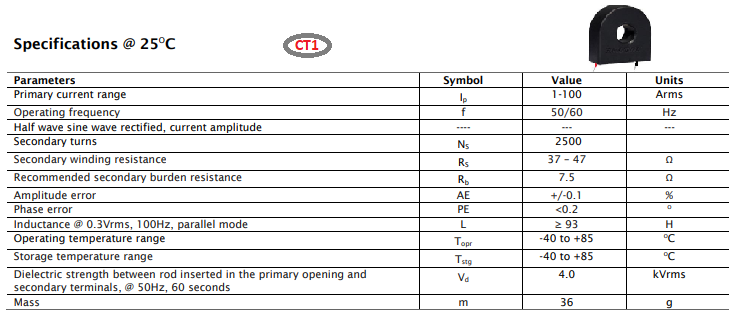

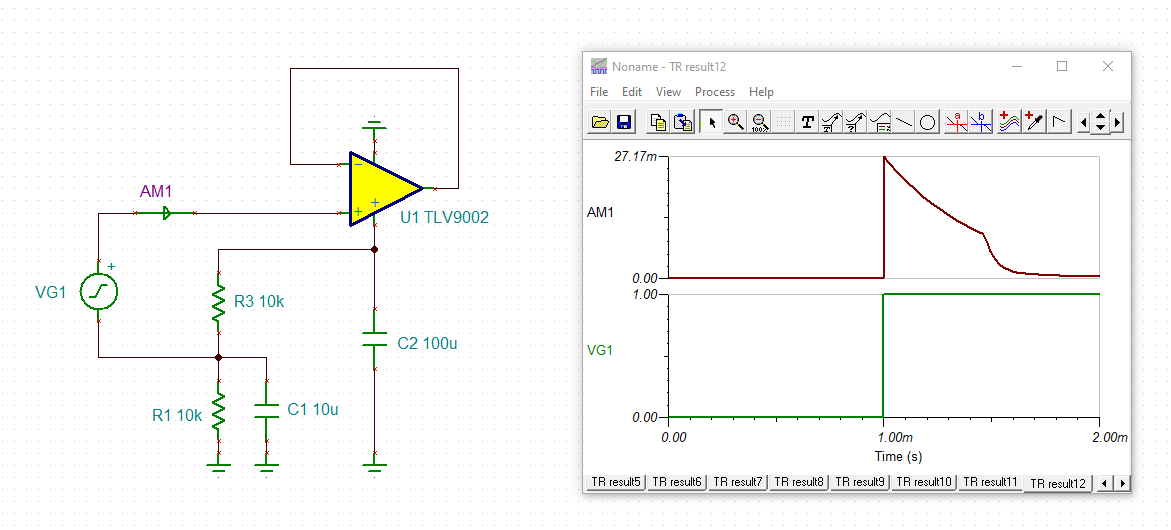

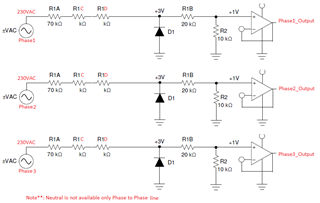

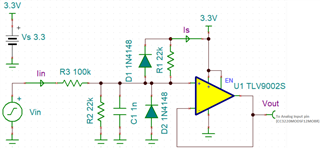

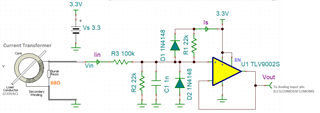

Our doubt is, Can we connect Current transformer for the same schematic as shown below? Any modification required or existing Schematic will works fine?

Thanks and regards,

Naveen K