Dear TI members,

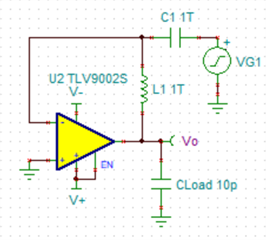

I did simulation with TINA for TLV9002 voltage follower but, the result of AC transfer characteristic analysis is wrong.

could you review my simulation setting or circuits ?

Best regards,

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Dear TI members,

I did simulation with TINA for TLV9002 voltage follower but, the result of AC transfer characteristic analysis is wrong.

could you review my simulation setting or circuits ?

Best regards,

Hi Hyun,

Kai is correct, the op amp output is saturated.

I always recommend running a DC nodal analysis to verify the output is not being driven into the rails.

Please let me know if you have any questions.

Best,

Jacob

thank you for reply it.

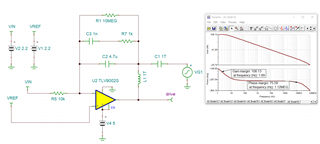

actually , I want to simulate stability of integrator circuits. I've draw circuits like below and i think the result is so wrong.

could you review my simulation setting or circuits ?

Dear jacob

I have a question. How can I know that there is output saturating or not in case of (+) input is 0V.

I can't find output voltage limitation at TLV9002 datasheet.

Best regards,

Hi Hyuan,

the output is again in saturation. Check the circuit by running a DC analysis.

The reason for the output saturation now is that your DC gain is infinitely high. To make the simulation run properly you have to add a high ohmic feedback resistor to set the DC gain to an acceptable level:

Also, "Vref" must be set to "Vin", otherwise you would amplify a DC input signal (2.5V - 2.2V = 0.3V) with the high DC gain, again driving the output into saturation.

Kai

Hello Hyun,

There are many ways to understand if the output is saturating. Firstly, think of what you are asking the op-amp to do. In the case of your first circuit, you are asking the amplifier to drive to 0V, yet setting V- to ground. All amplifiers will require output headroom from the supply rails to operate linearly.

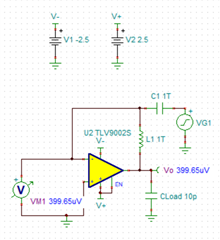

If this method is too challenging to utilize, you can always measure the voltage difference at the inputs of the amplifier. In DC linear operation, these inputs should be approximately the offset voltage of the device. See the change in VM1 voltage for both circuits below.

Bad:

Not Bad:

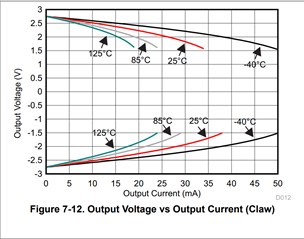

As for datasheet specification, the term somewhat varies depending on the device (VOL, VOH, Output swing). Recall, output swing varies with output current, so the claw curve of the device is usually a good bet for understanding how close to the rail the amplifier can swing:

We also specify typical swing from the rail when configured in a typical test circuit (10k load with mid-supply Vcm):

![]()

Please let me know if you have any questions,

Best,

Jacob

Dear Jacob

I have one question.

If V(+) is 5V and V(-) is 0V , TLV9002 can output from V(+) - 10mV and V(-) + 10mV ? (RL = 10k , typical Vo)

Dear kai,

thank you for reply.

I have 2 questions.

(Q1) I did simulation as your advice , phase margin is stable (76 degree) but gain margin is unstable (108dB) .

In order for the system to be considered stable, shouldn't the gain margin be negative?

How can i understand result of gain margin ?

(Q2) As I know, C2 and R7 is for stability fine tuning . I did change C2 (100nF -> 1nF) and R7 (100k -> 1k) but there is no change bode plot curve.

please review this case .

Best regards,

Hi Hyun,

If V(+) is 5V and V(-) is 0V , TLV9002 can output from V(+) - 10mV and V(-) + 10mV ? (RL = 10k , typical Vo)

This is only the output saturation voltage. The OPAmp will not run in its linear operation range when hanging in output saturation. To make the OPAmp run properly you should look at the "open-loop voltage gain" specification in section 7.10 of datasheet. And this says that you should stay 50mV away from the supply rails.

I did simulation as your advice , phase margin is stable (76 degree) but gain margin is unstable (108dB)

Hhm, I don't know what you mean. The negative scale on the vertical axis is a simulation artefact. Add to all phase values 360° and everything will be fine. It's fully normal for a standard OPAmp that the phase goes to +180° at very low frequencies.

Kai

Hi Hyun,

As I know, C2 and R7 is for stability fine tuning . I did change C2 (100nF -> 1nF) and R7 (100k -> 1k) but there is no change bode plot curve.

I don't see any effect on the performance of this circuit. Where do you have this circuit from?

Kai

Hi Hyun,

Can you share the goals for your circuit (Integration frequency range, and gain requirements)

The circuit you designed looks stable to me.

The Analog Engineer's Cookbook contains a guide for designing integrators, link here: Integrator circuit

I find this guide to be helpful for selecting components and amplifiers for realizing a functional integrator.

Best,

Jacob

Dear Kai,

this is for IRIS control circuits of Lens and receive from SoC vendor just for reference.

the net name "DC_IRIS_PWM" is input signal to opamp and the PWM has 25kHz frequency and variable on duty as outside brightness.

if brightness is so large , DRIVE+ voltage will be decreased by increasing PWM on duty .

I'm just want to know about stability of integral circuits and the role of around passive element (R , C) along feedback line.

anyway, below circuits is good simulation model for stability check. right ?

what do you think about the role of C3, R7 ? I was thought C3, R7 is compensation element for tuning stability but the simulated result is not followed by C3, R7 changed value.

Best,

Hi Hyun,

this cannot be answered with certainty without knowing the load in detail.

It doesn't seem to have to do with phase stability but it could be an equalizing scheme to modify the frequency response at the low frequencies or the relict of such an equalizing scheme.

But why not asking the manufacturer who gave you this circuit?

Kai

Hi Hyun,

I agree with Kai, I was unable to find any significant influence to stability in implementing C3 and R7.

Please let me know if you have any further questions.

Best,

Jacob