Other Parts Discussed in Thread: TINA-TI

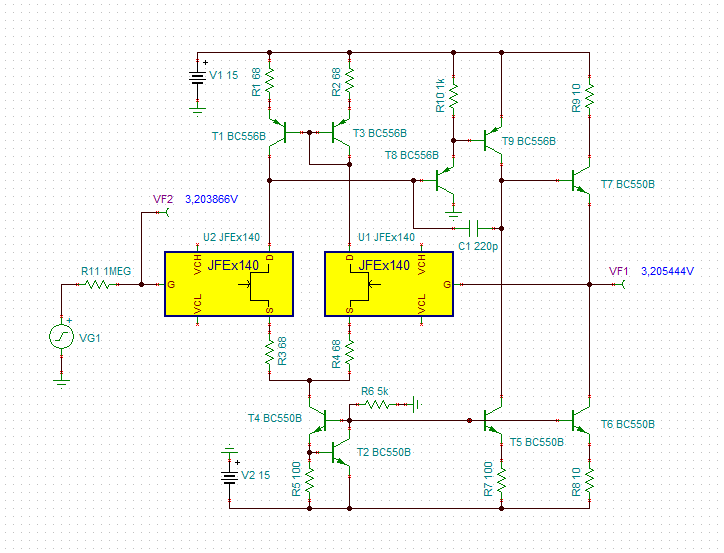

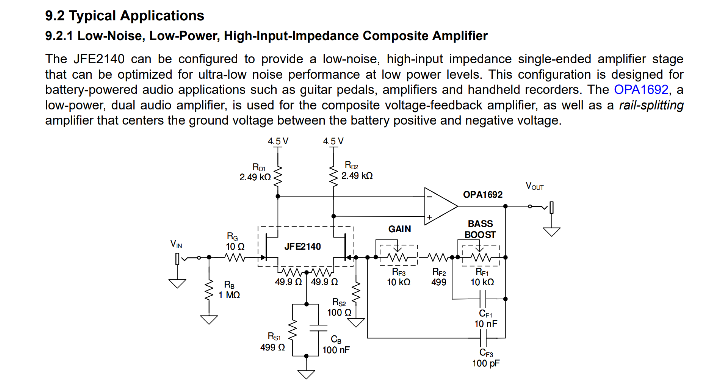

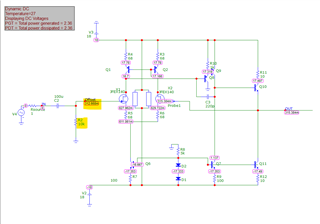

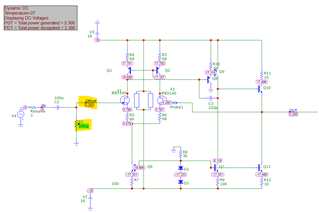

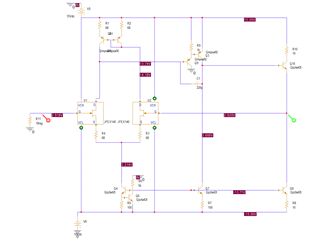

I'm working on a discrete operational amplifier for audio purposes, and the JFE2140 seemed well suited as an input stage. However, on importing the model into my preferred sim, Microcap 12, I saw atypically high input offsets.

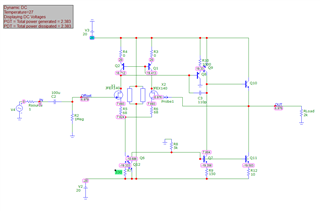

I was able to approximately replicate this behavior in PSpice for TI

and so I do not believe it reflects an error in the import or simulation software.

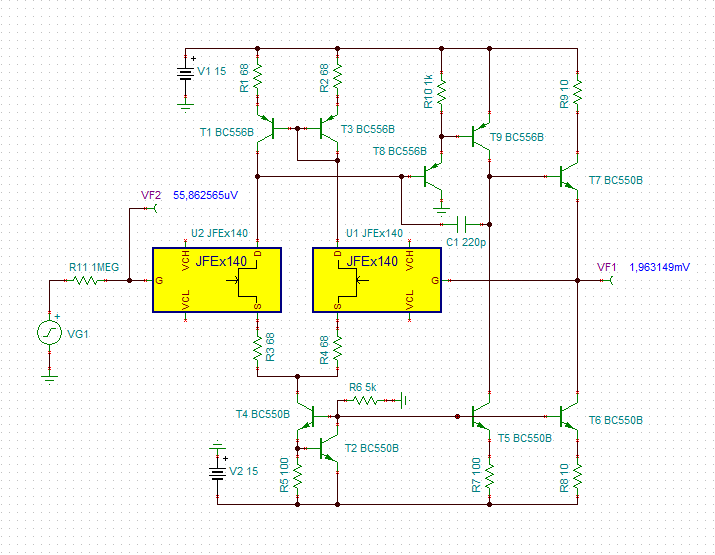

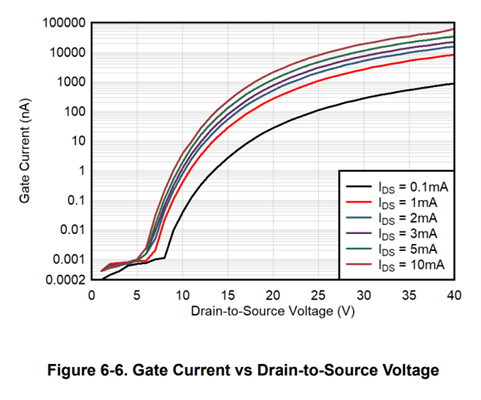

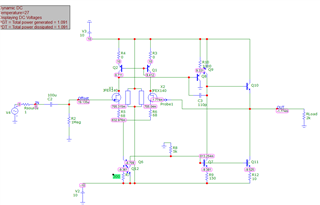

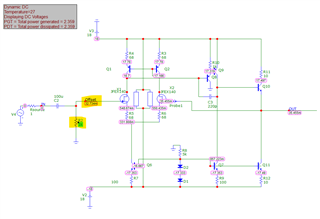

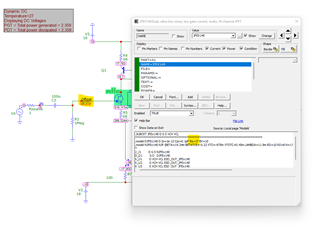

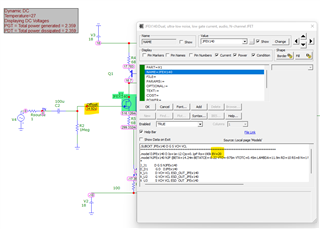

Changing the integrated diode Rs

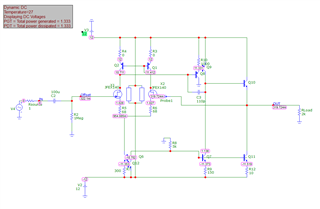

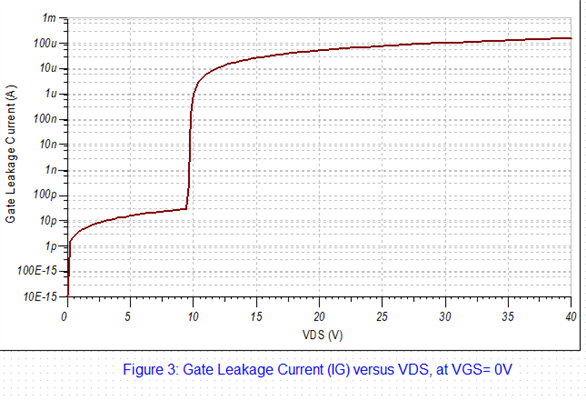

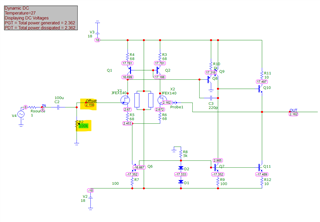

and breakdown voltage

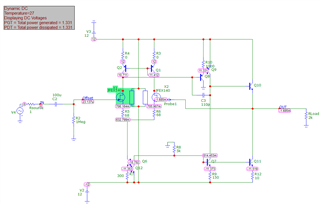

both appear to restore correctish behavior per the datasheet - is it possible to check if the values in the current .lib are correct?

I will note that this fix works even with the diodes floated, and floating the diodes does not seem to impact the offset behavior in SPICE in my testing.