Part Number: THS4631DDAEVM

Other Parts Discussed in Thread: THS4631

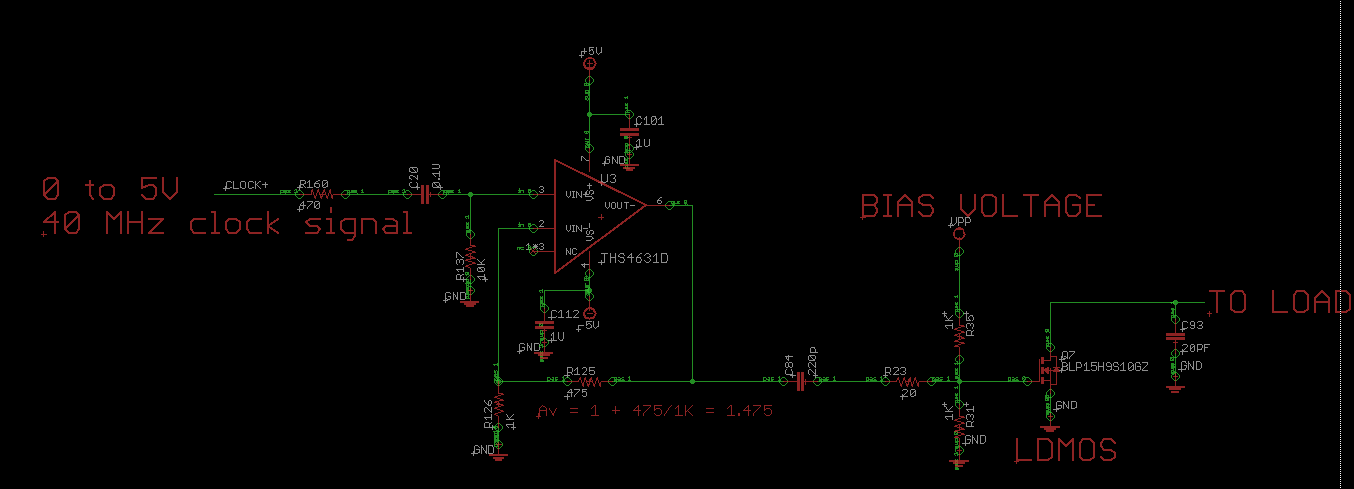

In the circuit below, I send short trains of pulses (0 to 5V) at 40MHz into the CLOCK+ pin.

The signal looks good at this point. However, on pin 3, the clock signal begin to look crazy as I increase VPP (my DC bias voltage on the LDMOS)

When Vpp = 1.5V, the voltage at pin 3 starts randomly shifting up and down with some dc offset, and sometimes the clock signal disappears for short time, and then turns back on?

I can't understand what is going on, I would think the input impedance at pin 3 would not be changing so I don't understand how the signal at pin 3 can suddenly drastically change.

Anyone have any insight?