Hi

I'm Joe GZ FAE and my account is SAJ.

Good to see that in the new inverter project of my account, SiC FET is used to build the power stage, that means we can study the system effect of the SiC FET, but not only limited to the device itself.

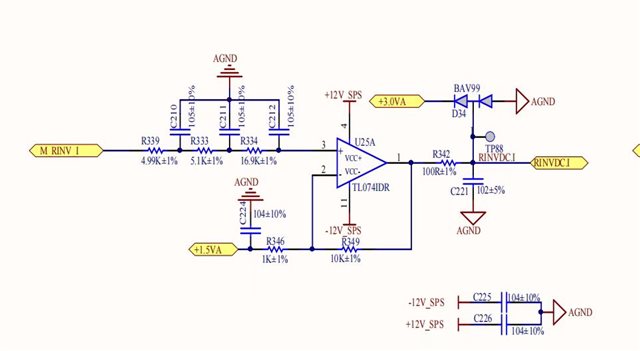

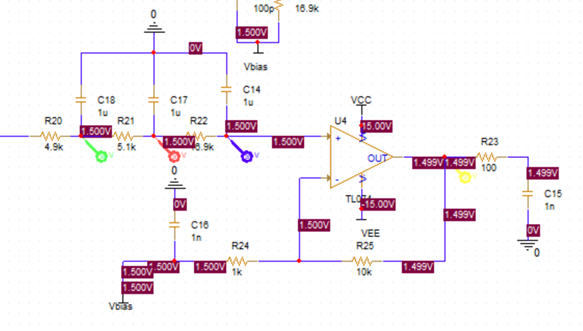

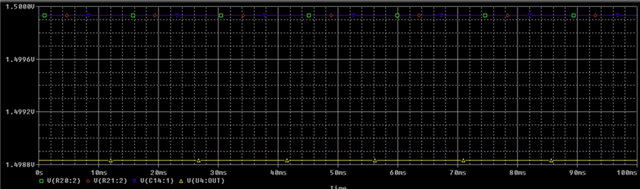

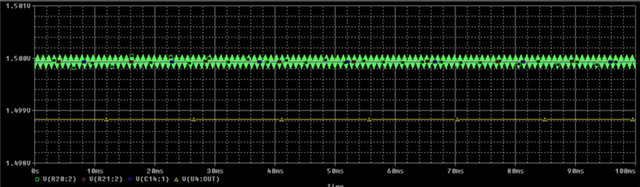

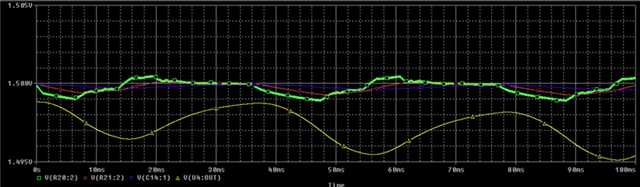

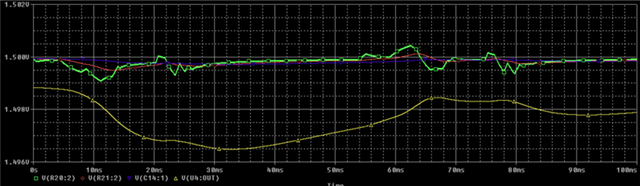

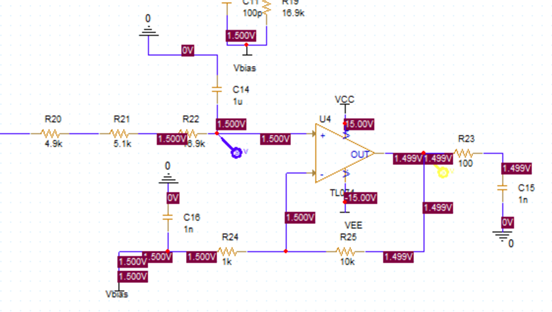

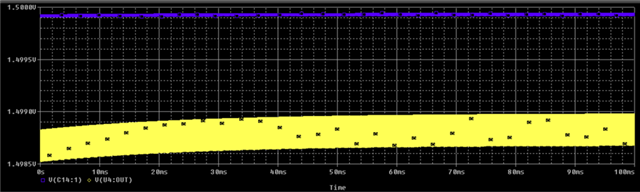

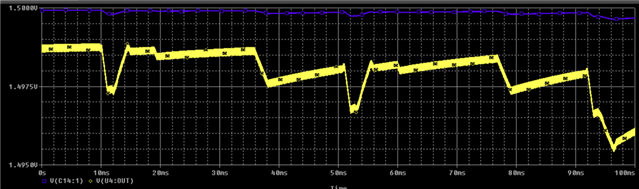

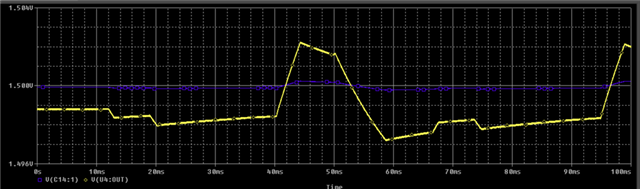

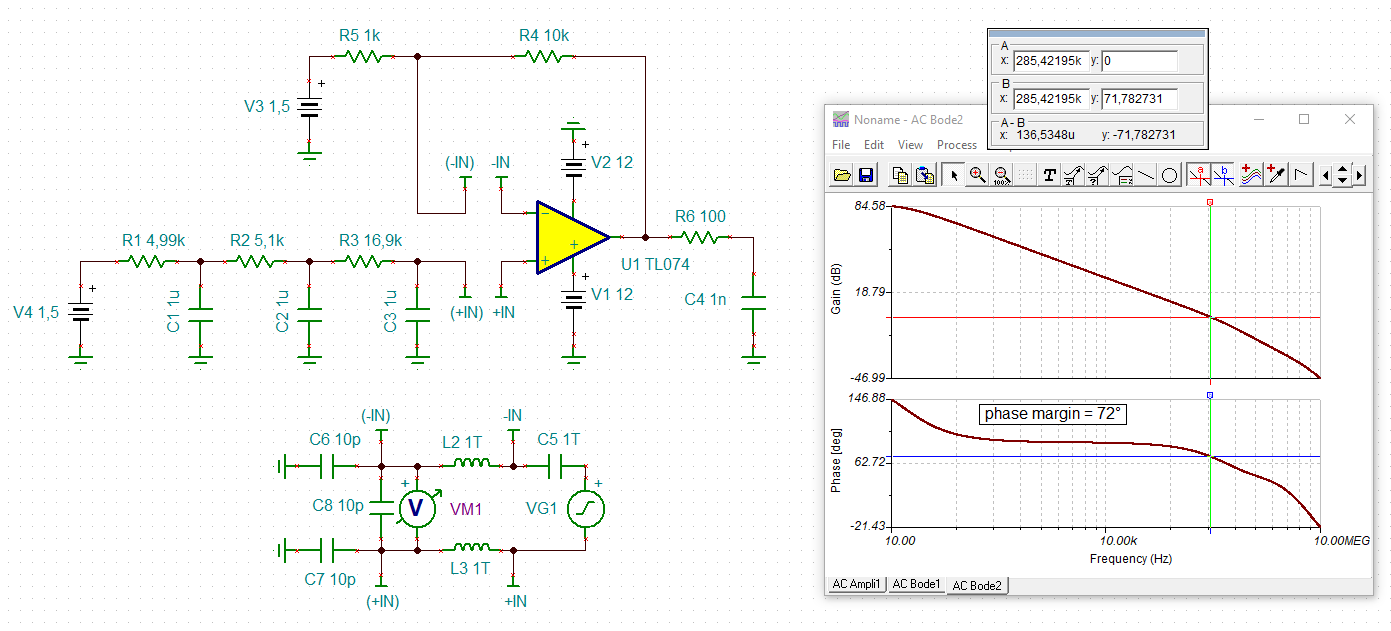

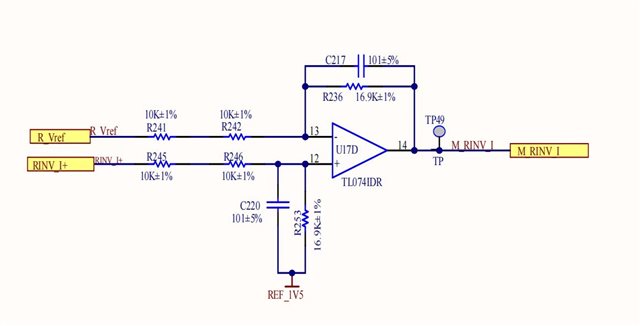

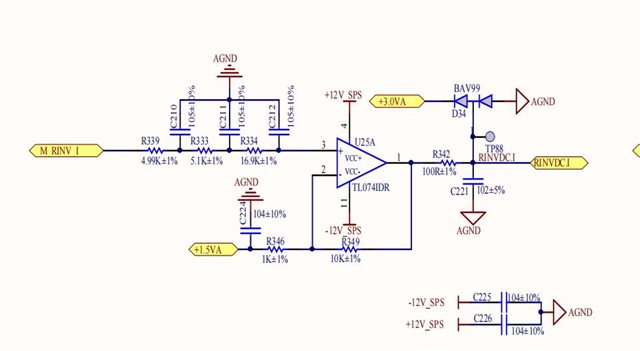

Now i meet the problem that when using SiC FET, the ultra short turn on and turn off time period causes a very high frequency noise which run through the PCB board and effect the input of TL074.

It causes a high common mode voltage between the positive input and negative input of the amplifier, and this should be suppressed through the circuit design.

the question is: the traditional differential amplifier circuit needs a high resistance accuracy to suppress the common mode input voltage so it is not practical. is there any practical circuit design which do not need the high accuracy resistance at the same time has a high CMRR?

thank you

BR