Other Parts Discussed in Thread: TIDA-01351, , TINA-TI, THS4504

Dear team,

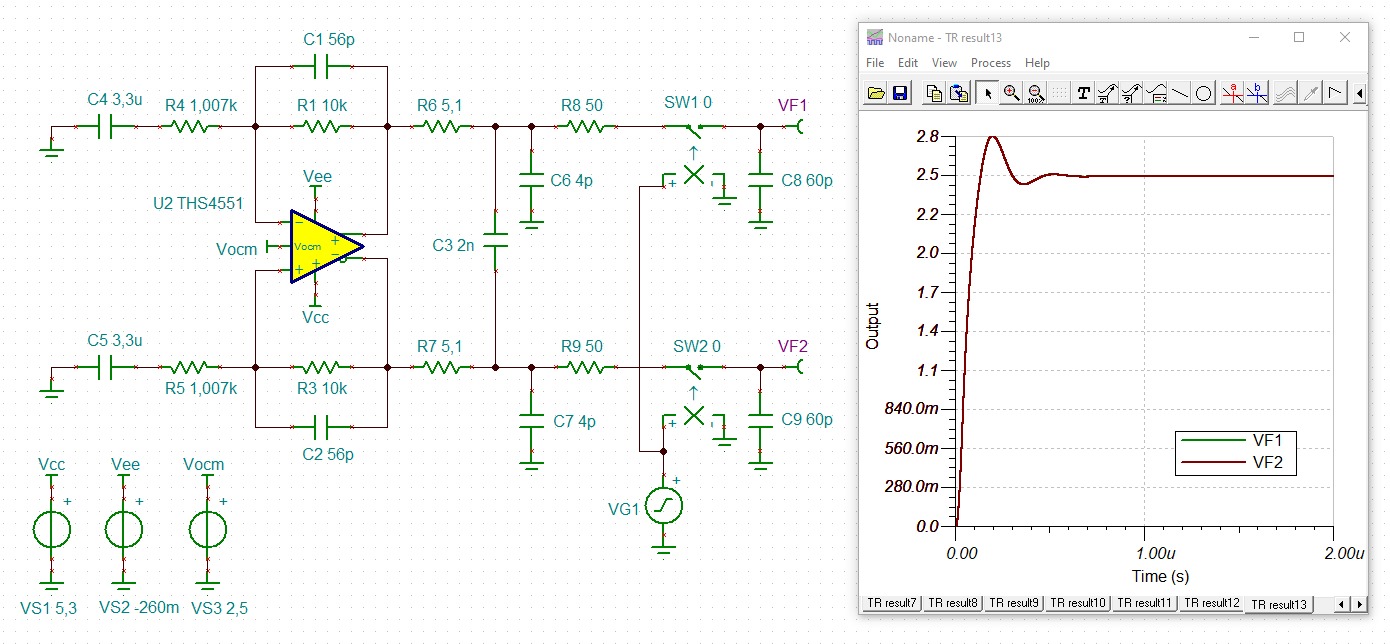

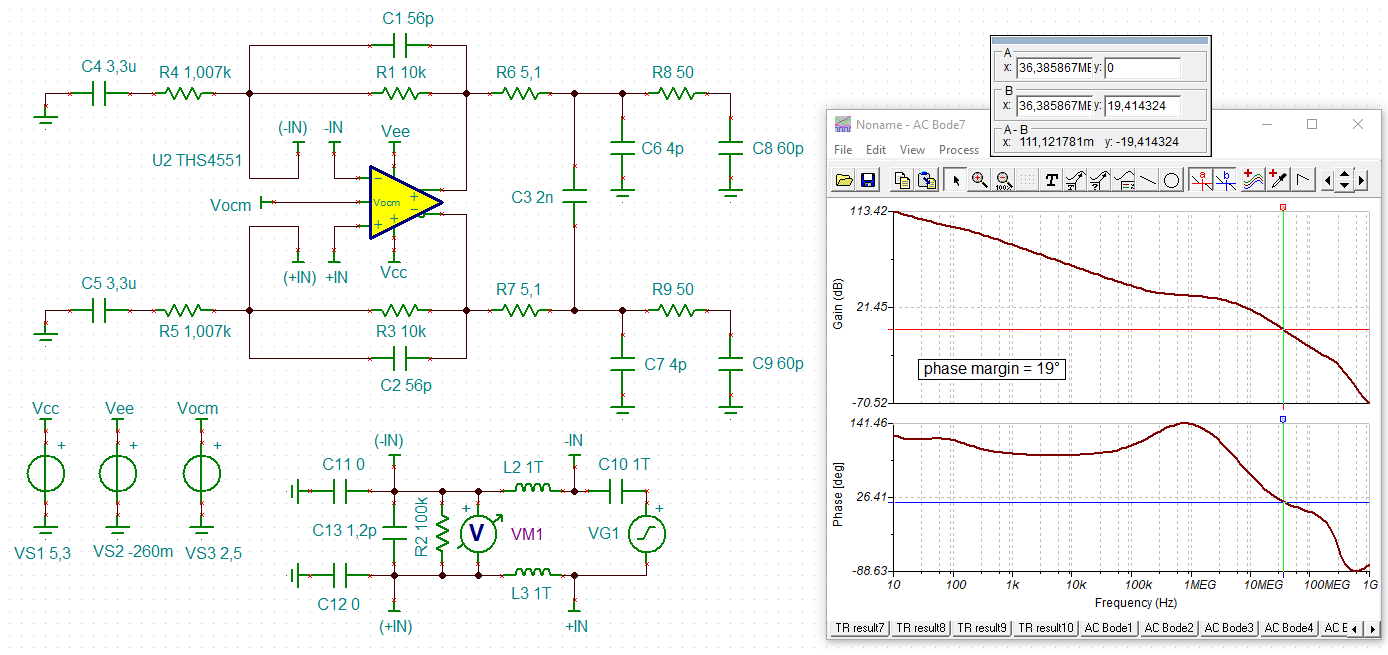

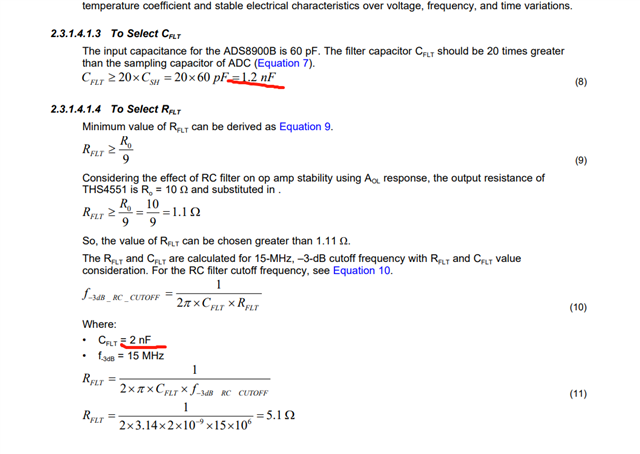

1. In the design guide of the TIDA-01351, the calculation result of the CFILT is 1.2nF, but in the later caculation, it is changed suddenly to 2nF, why? is that because the differential siganal so the CFLIT should be multiplied by 2?

2. In the design guide of the TIDA-01351, the gain of the THS4551 driver is set to 10V/V, so the signal gain of the THS4551 driver is just about 135/10 = 13.5MHz.But in the caculation below, the signal bandwidth of the driver needed to settle the ADC is about 15MHz. Is the margin of the BW too small to settle it ? or am I evaluate the siganl bandwidth of the driver and the bandwidth needed to settle the ADC uncorrectly.

Looking forward to your suggestion.Many thanks!

Ultrasound CW doppler design.pdf

Ultrasound CW doppler design.pdf

Best Regards

Zhihong Huang