Slave address setting can set 16 addresses depending on what is connected to A0 and A1 pins. (equivalent to 4bit)

There are four connection destinations: GND, VS (power supply), SDA, and SCL.

SDA and SCL are signals for I2C communication.

(1) When the address is specified using SDA and SCL, when is the address determined?

When specifying (write operation) to INA231, how long should I wait after VS rises?

(2) Please tell me whether the slave address does not depend on the logical values of SDA and SCL.

(3) If there are restrictions such as the rise time of the power supply VS, the rise time of SDA and SCL, please tell us what they are.

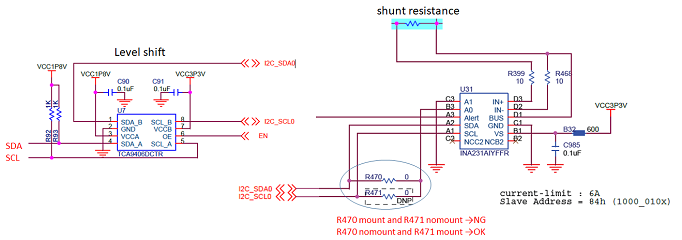

We are currently developing a board with three INA231s.

Each slave address is designed as A0=SDA/A1=GND, A0=SDA/A1=VS(3.3V), A0=GND/A1=VS(3.3V).

Please let me know if there are any hardware or software restrictions such as those mentioned above.