Hello Texas Instruments,

1) If AVDD and DVDD are both 3.3V same exact voltage regulator part number but two different parts. Could this be a problem? Page 41 says make AVDD above DVDD so V out does not raise AVDD. I assume they will be within 10mV.

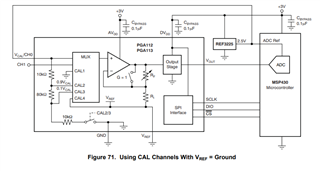

2) What is the difference between binary and scope gain? I do not understand this and it is mentioned throughout the datasheet.

3) What does the read command do? Check Table 4 for more info.

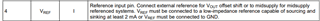

4) If DVDD = AVDD = 3.3V is CH0 Reference a 3.0V reference ok?

5) Can you confirm that VOUT is low impedance output capable of driving ADC?

Thank You For Your Time.