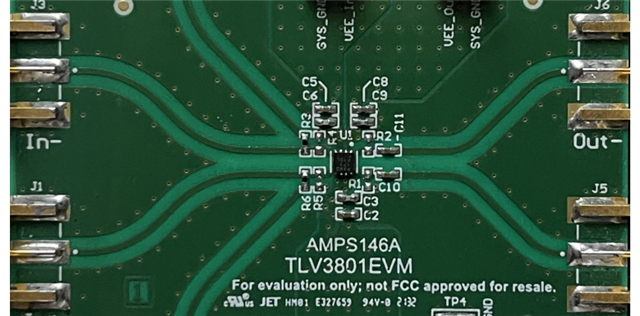

Other Parts Discussed in Thread: TLV3801, TLV3811, TLV3801EVM, TLV3601

Output is square wave for input below 200 MHz and sawtooth when input greater than 200 MHz. Is this expected ?

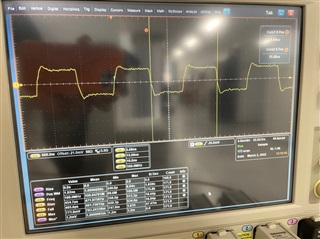

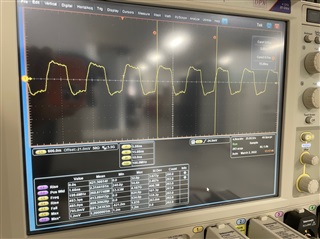

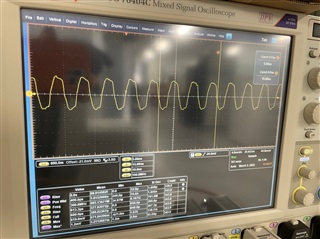

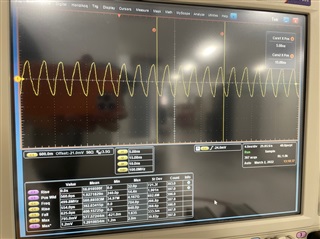

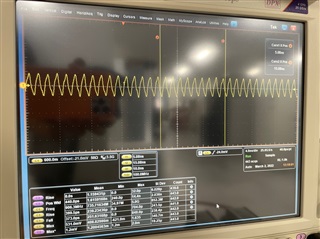

Below are screenshots of TLV3604 outputs are different input frequencies -

1. 100 MHz sinewave input

2. 200 MHz sinewave input

3. 300 MHz sinewave input

4. 500 MHz sinewave input

5. 900 MHz sinewave input

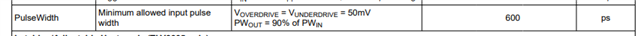

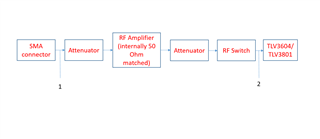

In the final application, the input to TLV3604 will be pulses, as narrow as 1 ns, from photo-multiplier tube or ion detector and the output from the comparator will be sent to an FPGA for counting. My questions are -

1. Is the behavior described and depicted in the screenshots above expected ?

2. If the behavior is expected, could you please recommend any other comparator part number that can go as fast as 1 ns.

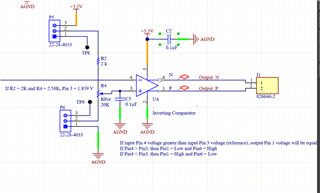

3. If the behavior is not expected, what could be some of the reasons for this ? I'm attaching the circuit schematic we're using and would appreciate feedback on it.

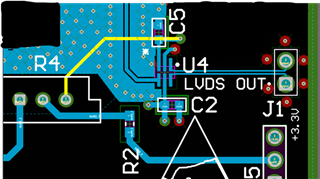

This circuit is completed in a 4-layer layout and fabricated. Please find layout screenshot attached here. In the screenshot –

- The Top layer (1) is blue, Ground (2) is green, Power (3) is red and Bottom (4) is yellow.

- Input to TLV3604 (U4) pin 4 is single-ended coplanar 50 Ohm controlled impedance and has shielding vias on either sides. The reference ground plane for top layer is layer 2.

- Pin 1 of R4 pot is connected to ground .

- J1 is a two pin male Molex header surrounded by ground vias.

- All measurements are done by a scope with 100 Ohm differential probes.

- C2 is bypass capacitor for pin 5 placed as close to U4 as possible. It is 0.1 µF ±10% 50V Ceramic Capacitor X7R 0603 (1608 Metric).

Capacitor C5 is 0.1 µF ±10% 50V Ceramic Capacitor X7R 0603 (1608 Metric). I tried removing it from the board and the LVDS output looks the same as before where it was a square wave for frequencies below 200 MHz and sawtooth for frequencies above 200 MHz.

For prototype testing, the input is a sine wave but for the end application, the input will be short pulses with 1 ns pulse width.

Could you please provide feedback on how to achieve faster rise and fall times as close to the datasheet spec as possible. Please let me know if I can provide additional details. Thank you