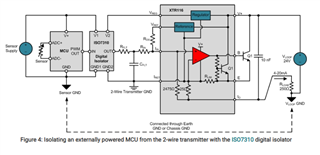

Other Parts Discussed in Thread: , XTR116

Hello TI team,

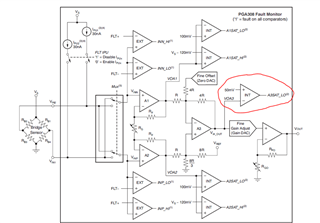

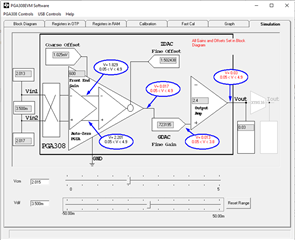

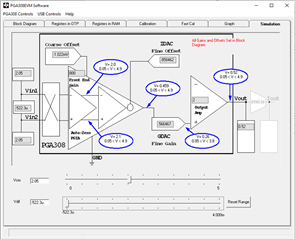

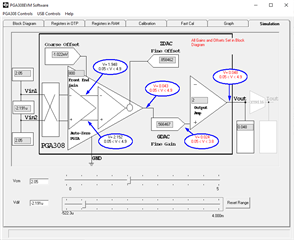

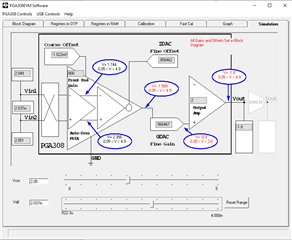

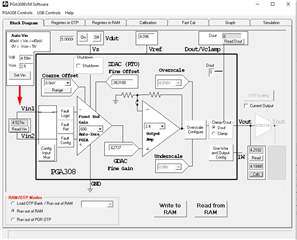

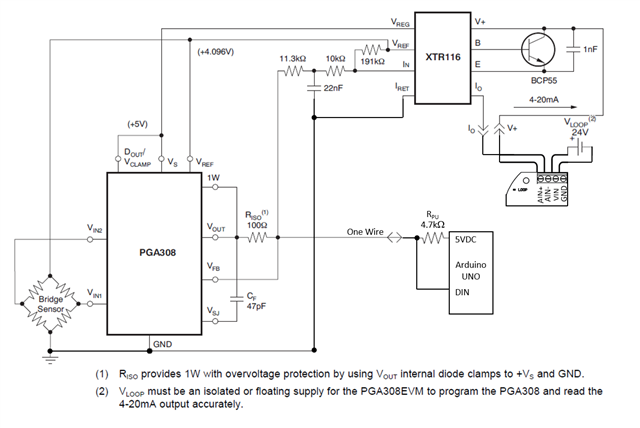

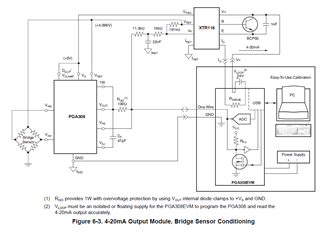

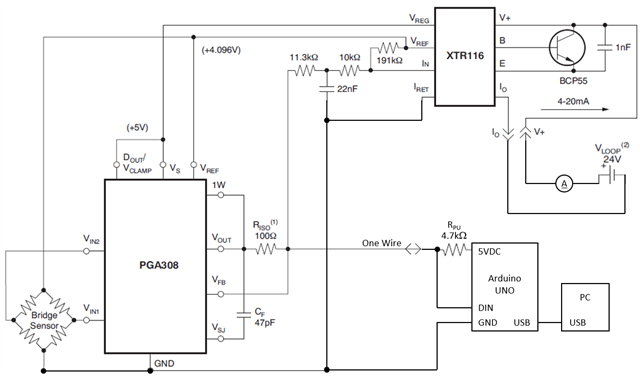

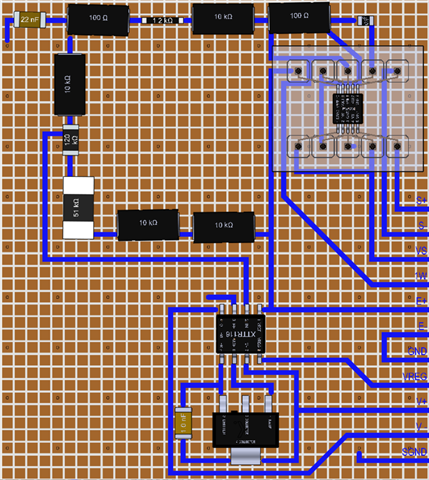

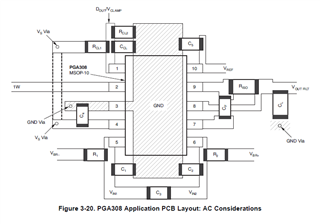

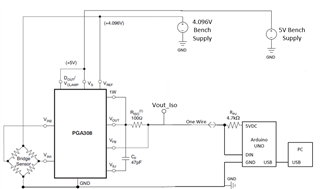

My application is very similar to Figure 6-3 of your publication “SBOU069B–June 2009–Revised January 2012” (i.e. TI PGA308 User Guide).

The only exception is the PGA308 is interfaced over 1 Wire via an Arduino Uno instead of the PGA308EVM.

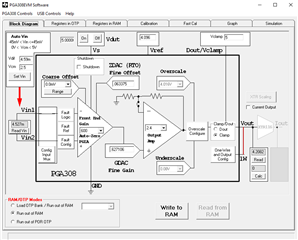

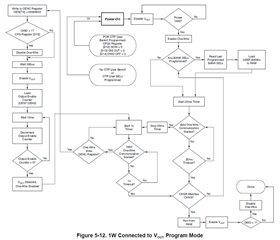

The PGA308 is operating in Virtual Software Mode according to Figure 5-13 of the aforementioned publication.

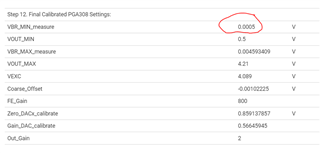

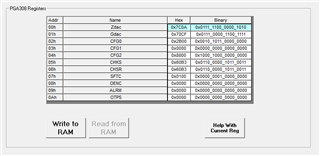

Here is the output read from the microcontroller:

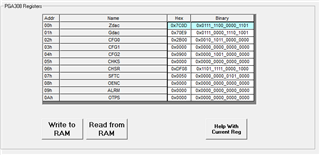

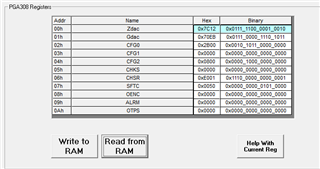

TIFL Register Value: 1100 1100 0000 0000

ZDAC Register Value: 0010 0001 0001 1001

GDAC Register Value: 1001 0101 1011 0101

CFG0 Register Value: 0011 1011 0000 0001

CFG1 Register Value: 0101 0000 0100 0000

CFG2 Register Value: 0000 1000 0000 0000

CHSR Register Value: 1011 0101 1110 1111

CHKS Register Value: 1011 0101 1110 1111

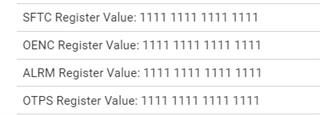

SFTC Register Value: 1000 0000 1000 0000

OENC Register Value: 0000 0000 0000 0000

ALRM Register Value: 0000 0000 0001 0000

OTPS Register Value: 0000 0000 0000 0000

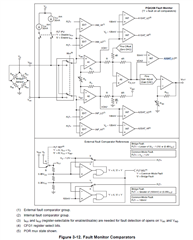

With this implementation the A3SAT_LO bit (ALRM D4) is indicating a fault condition and the current returning to the XTR116 V+ pin is not changing in proportion to changing load of the bridge sensor. The bridge sensor (a full bridge strain gauge load cell) is in working order as verified by an off-the-shelf load cell meter.

I read from page 40 of the aforementioned publication that: “The A3 amplifier in the Front-End PGA is also monitored for negative swing violations that can occur if the Zero DAC is incorrectly combined with the Front-End PGA gain select.”

I’m unable to figure out what if any error there is in the gain sizing & offset values.

I can send gain sizing & offset calculations in a direct email for your reference if required.

I have tried selecting FE_Gain on either side of the G_total but neither of these selections produce results that work.

Please advise on how the problem can be solved.

Thank you,

Robert Marvel

Electro-Mechanical Design Engineer