Other Parts Discussed in Thread: TLV1821, TLV1811

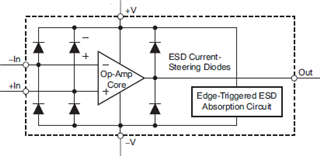

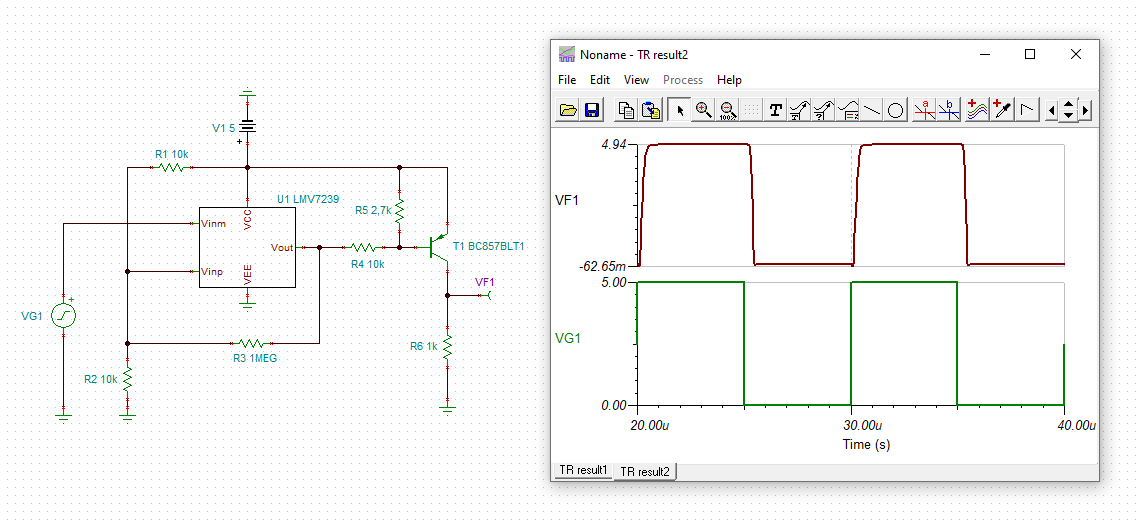

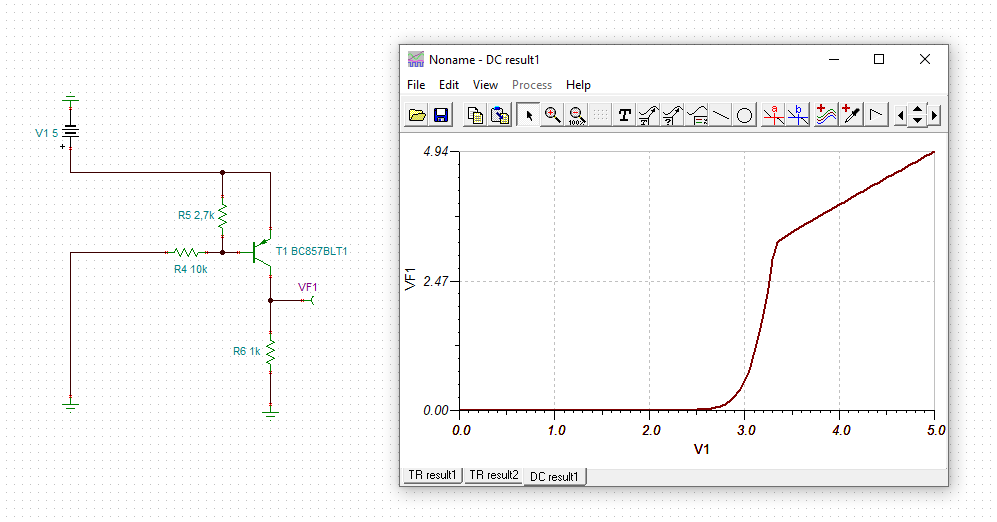

I have a design as given attached figure.

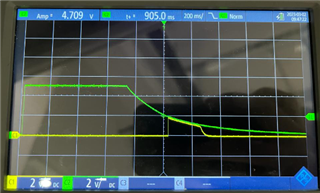

During power down sequence of 5V supply, comparator outputs peak nearly 2V amplitude with ~100msec decaying waveform.

As it is seen in the figure, signal is applied with (+) terminal is 0V level during power down and normally i was expecting 0V logic low output, contrarily.

What could be the reason and more importantly how can i solve this problem?

(i can make a design change if you recommend an adequate solution)

Best regards

İlhan