Other Parts Discussed in Thread: TL081

Hi,

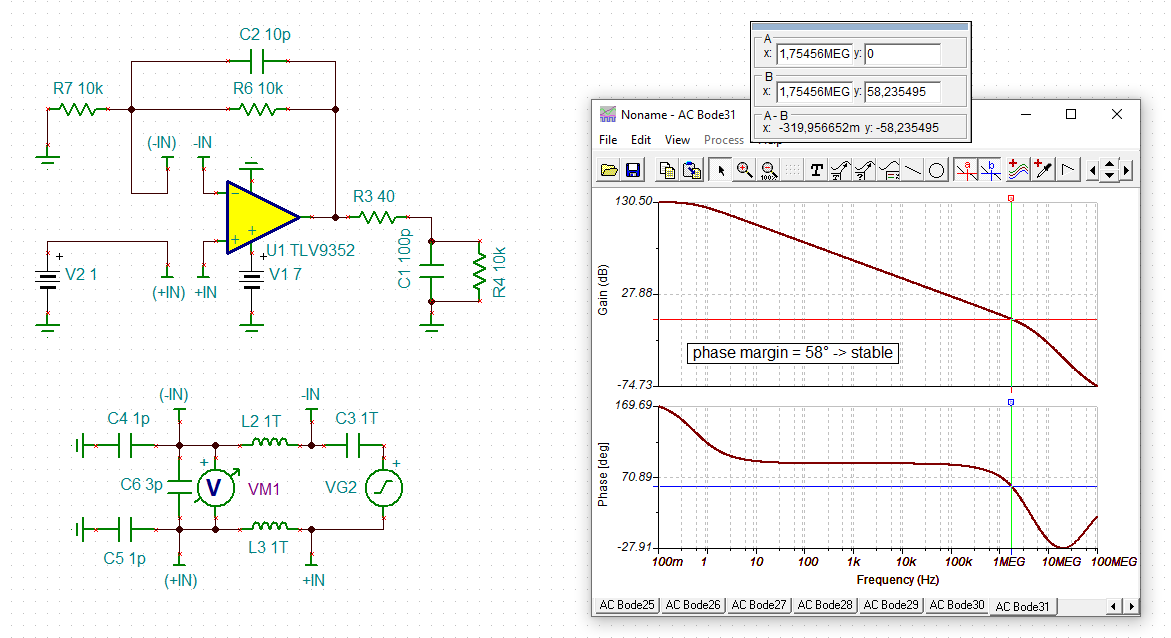

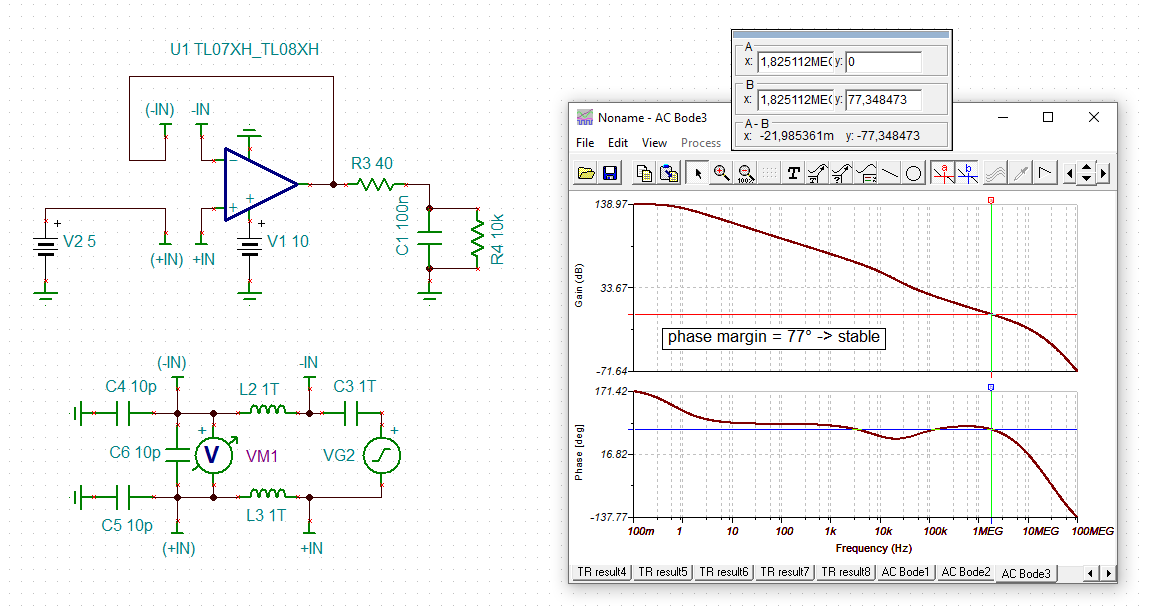

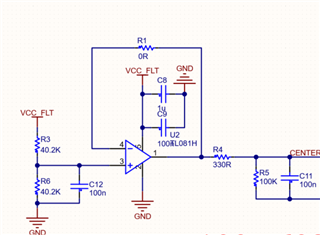

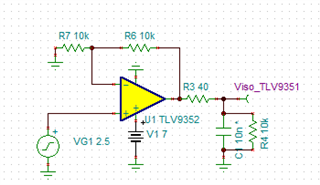

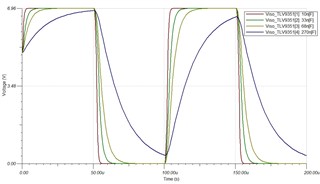

I am using TLV9351 to drive capacitive load with isolation resistor. The circuit schematic is attached.

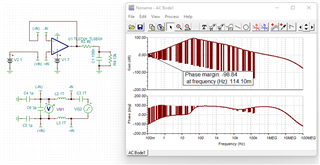

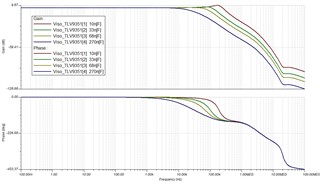

The simulation results are attached.

Cload Compensation_TLV9351_last.TSC

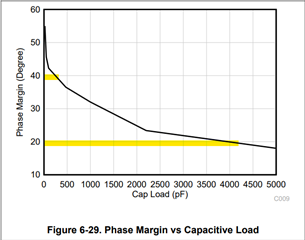

1.What is the maximum and minimum capacity can I use?

2. What will happen if I drive TLV9351 with 0-7V input voltage when the supply voltage is 7V? Can I drive it like that?