Other Parts Discussed in Thread: LF356,

Asking on behalf of customer.

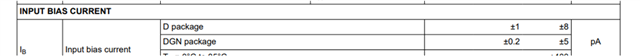

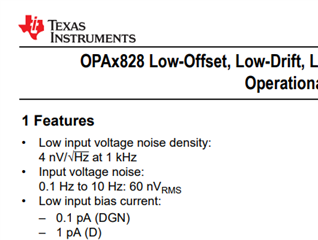

According to first page of datasheet, input bias is 10x different DGN package vs. D package.

What is driving this discrepancy?

Contact me internally if further details needed. Thanks!

-Steve