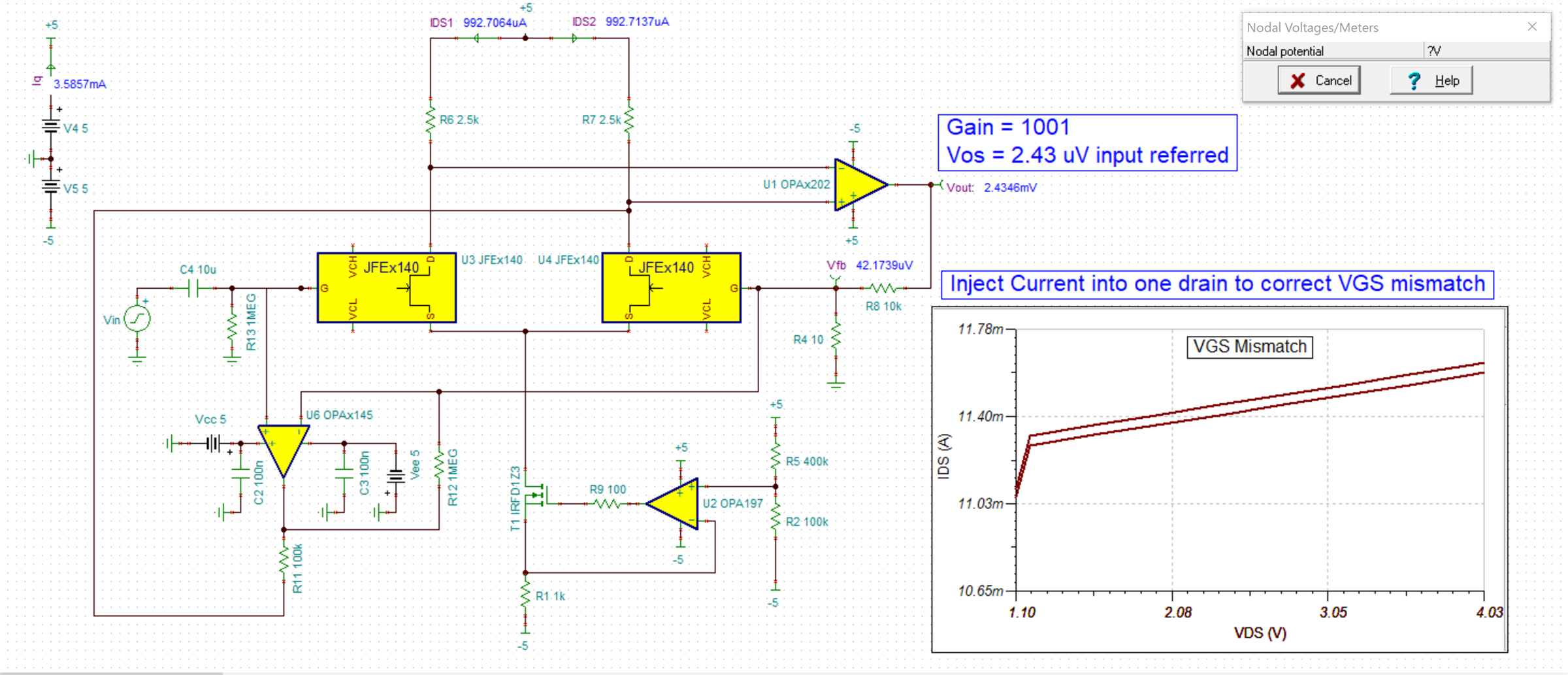

Other Parts Discussed in Thread: , OPA202, OPA145

Hi,

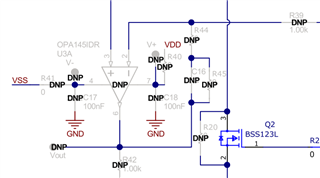

Is the offset correction integrator circuit (U3 & surrounding) in the JFE2140EVM actually tested working?

https://www.ti.com/lit/ug/slpu010/slpu010.pdf

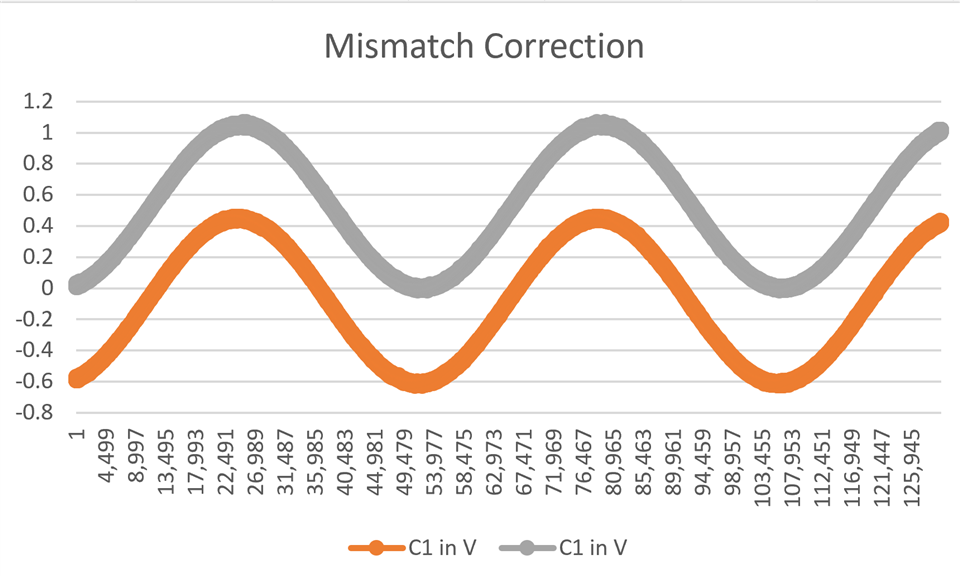

I've run a simulation with the offset correction integrator circuit inserted & it doesn't work.