Hello,

Looking for a validation of the circuit attached or a recommendation to improve further.

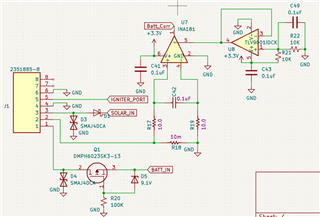

The picture shows a circuit using INA181 and TLV9001IDCK to sense current through a 12V battery. Pins 1 & 2 on terminal block J1 is a battery connector. The pin number 1 is the battery positive supply where a p-channel MOSFET is configured to protect the load from reverse polarity and pin number 2 is the battery negative supply where the INA181 is configured across a 10 milli ohm resistor for current sense.

Please have a look at the schematics attached and let me know your thoughts.

Thanks,