Other Parts Discussed in Thread: OPA202, , JFE150

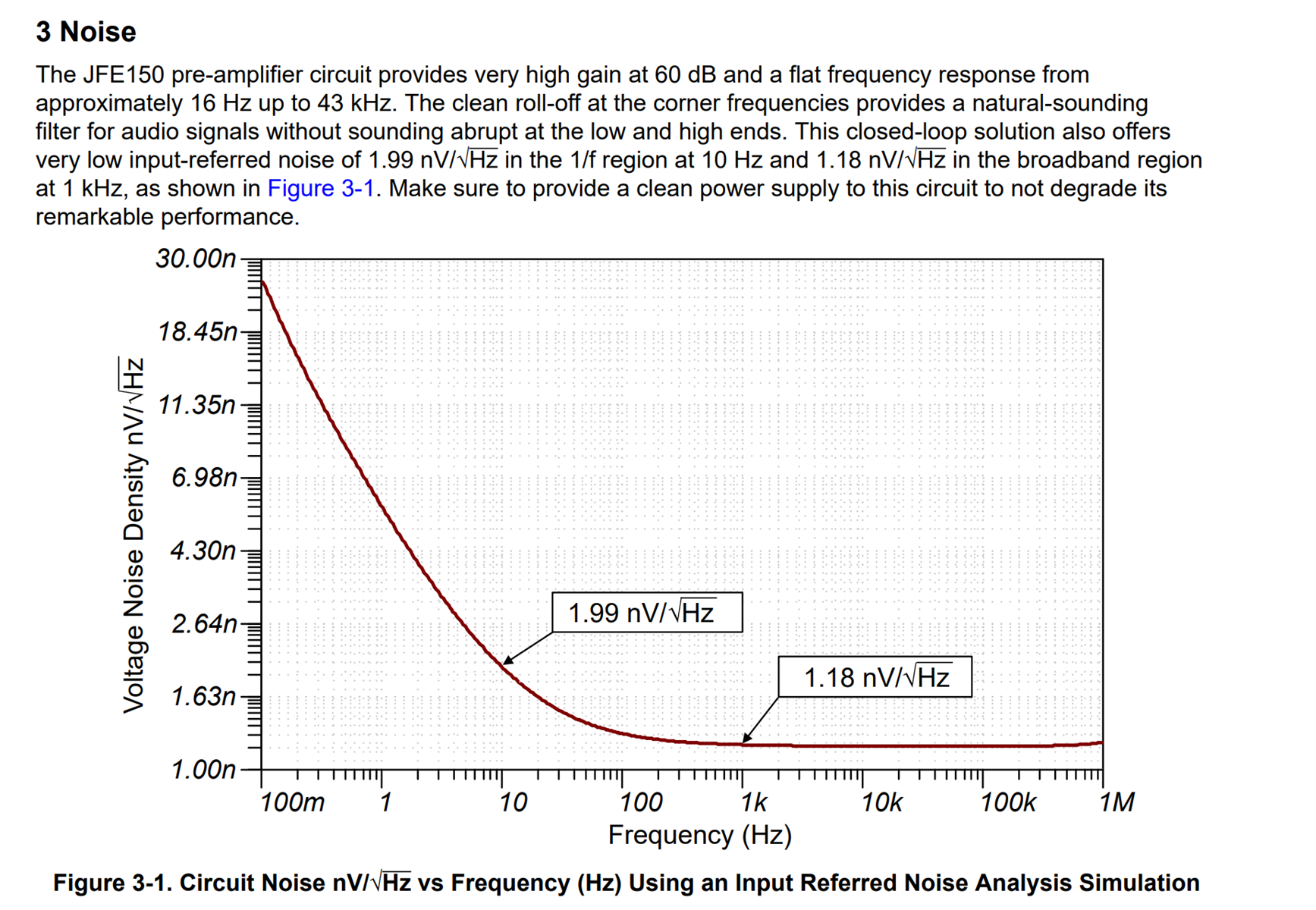

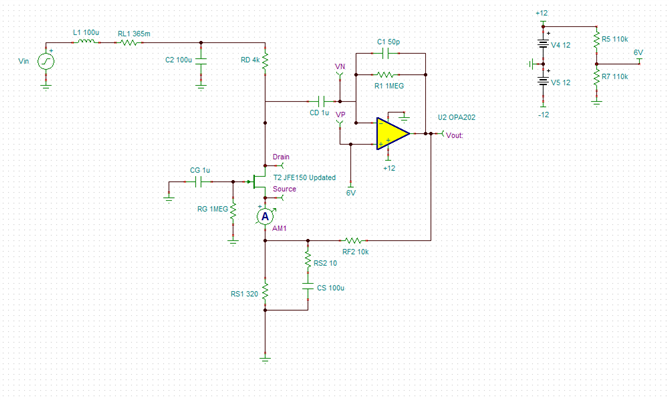

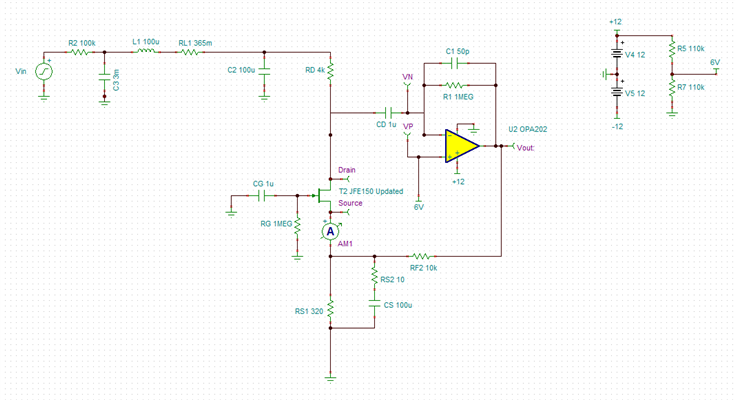

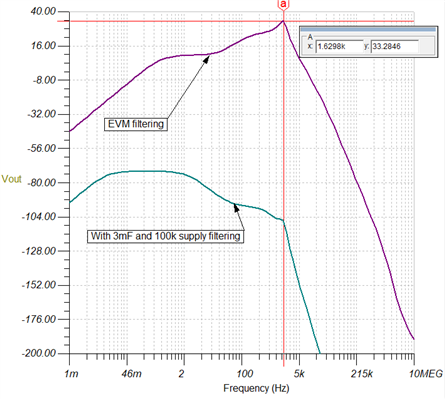

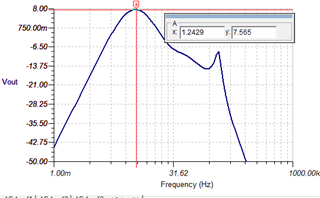

Hi, I note in the JFE150EVM there's an LC on the supply input, with a corner around 1 kHz or so. I'm wondering with 60 dB of gain how sensitive the Figure 4-1 circuit in the JFE150 Evaluation Module User's Guide might to supply noise? While the OPA202 has solid PSRR, the JFET configuration probably does not. In SPICE it looks like a 1 kHz tone injected on the 12V rail is mirrored almost 1:1 at the output, suggesting the supply might be a challenge. I'm looking at using a TPS7A series LDO with ~20 uV noise from 10 to 100 kHz for the +12V.

Thanks for any guidance