Part Number: LMH6629

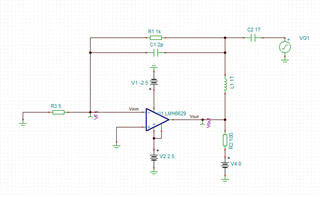

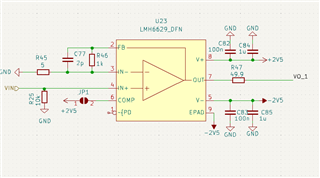

Hi I'm having issues with a large negative offset appearing at the output of the LMH6629. I have attached an image of the circuit schematic

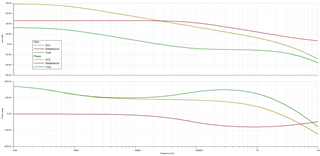

LMH6629 is setup in a +/- 2.5V bipolar configuration. in the 4 V/V mode. I am using the DFN package with the feedback pin. Please note that the source resistance is 260 ohms, and it isn't indicated on the schematic.The cutoff frequency is around 8MHz. For another reason I not understand, 2pF gives this cutoff instead of the 20pF one would expect from calculating 1/2piRC. Is this due to the internal compensation in 4 V/V mode?

If I am correct, the offset should be calculated(in Latex for ease of viewing) via Vo = 1+ \frac{R_f}{R_g}(V_{in}+ V_{os} +(I_{b+}\cdot R_s)) -I_{b-}\cdot R_f . This formula is calculated assuming the bias current flows out of the inputs of the amp. Therefore, in my configuration we should expect the larger source resistance to be the dominating factor in determining the offset, which should therefore be positive. I am however instead seeing a negative offset as mentioned, and quite a large one at that(up to -6mV referred to input)

My suspicion was that the impedance seen be the inverting terminal was far too low, as section 7.3.3 of the datasheet indicates it should be above 25 ohms. However, no matter the configuration I use, I always see a negative offset. I have tried to drastically reduce the gain down to even Av =15, to increase Rg up to 100 ohm, and to match Rs to Rg in parallel with Rf to reduce the impact from the bias currents. I even tried using the SOT-23-5 package but no difference.

Any thoughts or assistance would be greatly appreciated. Can clarify any points needed/add scope captures.