Part Number: INA234

Hi expert,

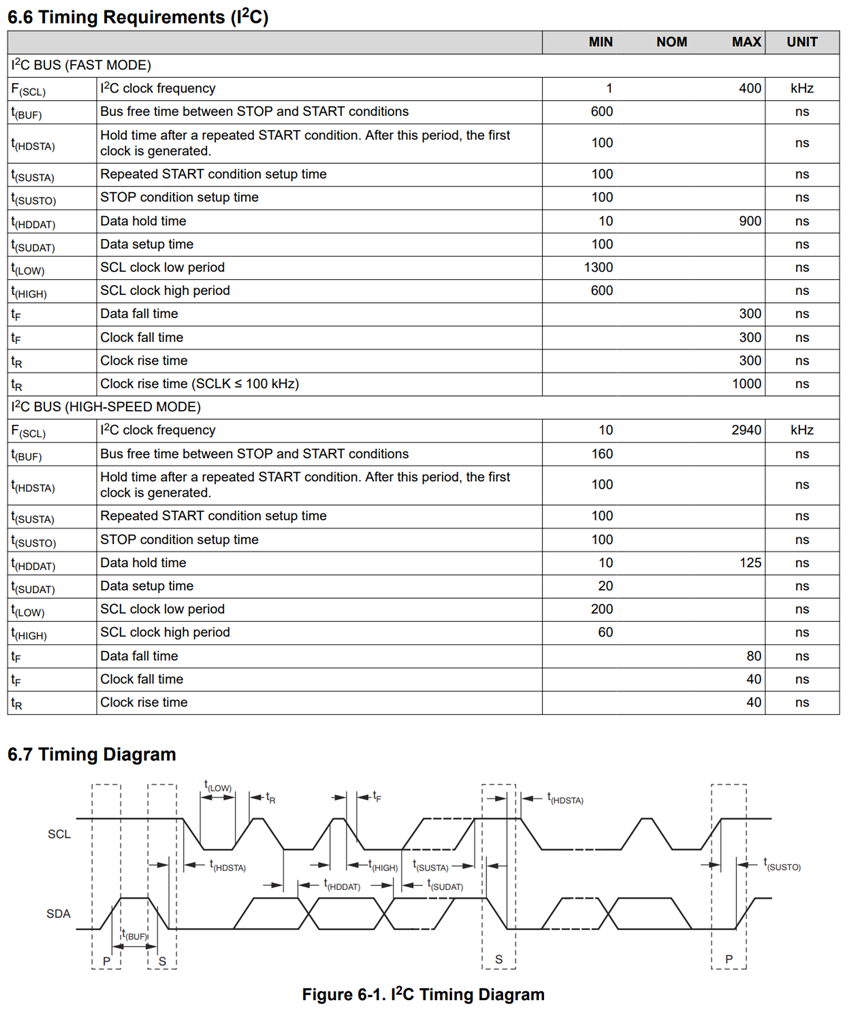

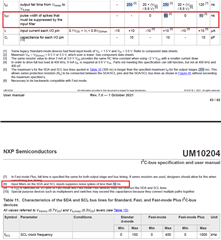

Could you please clarify if there is any risk for the I2C communication of INA234?

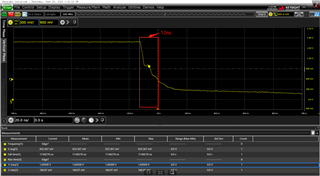

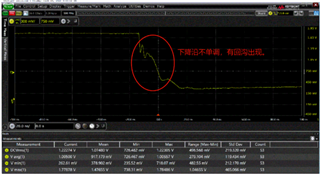

The falling edge is not smooth, and you can see up and down in below picture.

p.s. so far I2C communication has no issues.

Regards,

Allan