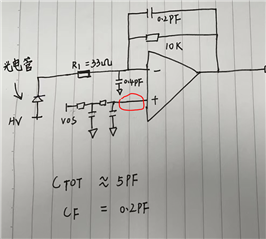

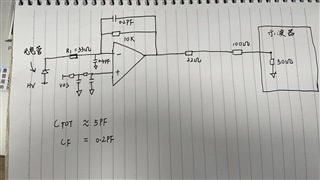

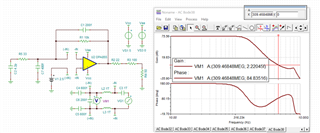

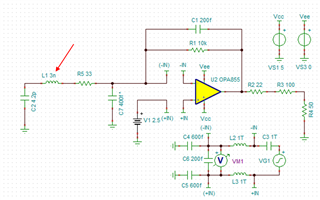

Our Customer Use OPA855 in a TIA circuit. Following is their test environment, right side for TIA is oscilloscope and the other is a photodiode.

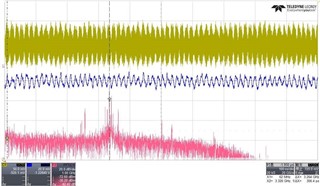

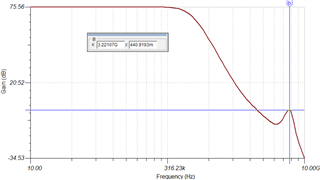

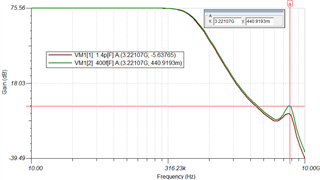

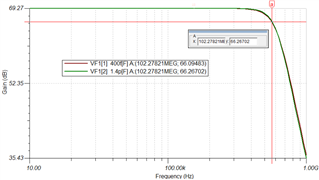

But there is a high frequency oscillation. Following is waveform, yellow is TIA output, pink is FFT frequency domain waveform. As the waveform shows, There is a 3.3GHz noise with a 100Mhz envelope signal. Customer changes the capacitance, but there is no effect.

What should they do to reduce the noise? Hope you could give they some method to avoid this.

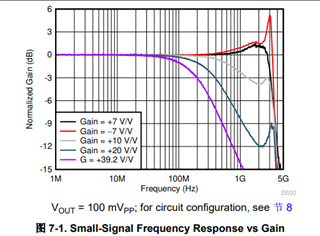

Hi, the datasheet shows when the state changes there will be an oscillate. And It seems is a 100MHz signal. Is this right? Is there is any way could reduce or inhabit the oscillate? The frequency is fix 100MHz?

Hi, the datasheet shows when the state changes there will be an oscillate. And It seems is a 100MHz signal. Is this right? Is there is any way could reduce or inhabit the oscillate? The frequency is fix 100MHz?